# Supplementary Material

## 1 NOISE MODELS

Currently, the hardware emulators in Qiskit support the following noise simulations: (i) gate errors, (ii) measurement errors, and (iii) decoherence in the form of thermal relaxation and dephasing. In this section, we discuss the noise modeling techniques used in these emulators (ibm, 2021a,b; Wood, 2020).

#### 1.1 Gate Error

Gate errors are modeled using depolarizing noise channel. During hardware calibration, error probabilities in every supported gate operation are measured using the Randomized Benchmarking (RB) protocol (Wood, 2020). In the emulators, the effect of gate errors is simulated using the bit-flip and phase-flip errors. The bit-flip and phase-flip errors are defined through the Pauli-X, Y, and Z operations. All three types of Pauli errors have the same probability to occur. The depolarizing channel is represented by the following operators:

$$K_{D_0} = \sqrt{1 - p1}I$$

$$K_{D_1} = \sqrt{\frac{p1}{3}}X$$

$$K_{D_2} = \sqrt{\frac{p1}{3}}Z$$

$$K_{D_3} = \sqrt{\frac{p1}{3}}Y$$

(S1)

Here, p1 is the error probability of a gate operation found through Rondomized Benchmarking (RB). The effect of the depolarizing channel on a qubit is expressed via the operator-sum representation, as

$$\rho_{in} \mapsto \mathcal{D}(\rho_{in}) = \rho_{out} = \sum_{i=0}^{3} K_{D_i} \rho_{in} K_{D_i}^{\dagger}$$

(S2)

Here,  $\rho_{in}$  is the density matrix of a qubit, and  $\rho_{out}$  is the output density matrix after application of the error channel.

#### 1.2 Measurement Error

During hardware calibration, the qubits are repeatedly prepared in the  $|0\rangle$  and  $|1\rangle$  states and the fraction of incorrect measurements are reported as the measurement error probabilities. In the emulators, the measurement errors are modeled as bit-flip errors (Pauli-X). This error channel is represented by the following Kraus operators:

$$K_{M_0} = \sqrt{1 - p2}I$$

$$K_{M_1} = \sqrt{p2}X$$

(S3)

Here, p2 is the measurement error probability of a qubit. The effect of measurement error on a qubit is expressed via the operator-sum representation, as

$$\rho_{in} \mapsto \mathcal{D}(\rho_{in}) = \rho_{out} = K_{M_0} \rho_{in} K_{M_0} + K_{M_1} \rho_{in} K_{M_1} \tag{S4}$$

### 1.3 Decoherence

The coherence times (T1 and T2) of the qubits are measured during hardware calibration. In the emulators, these coherence times and the gate execution times (Tg) are used to to model the impact of decoherence. Using these values, we can define the probability for each qubit to relax and dephase after a gate operation as  $p_{T1} = e^{(-Tg/T1)}$  and  $p_{T2} = e^{-Tg/T2}$ , respectively. We can then define the probability for a qubit to reset to an equilibrium state as  $p_{reset} = 1 - p_{T1}$ . When  $T2 \le T1$ , the relaxation and dephasing noises are represented by the following operators:

$$K_{I} = \sqrt{p_{I}}I$$

$$K_{Z} = \sqrt{p_{Z}}Z$$

$$K_{reset} = \sqrt{p_{reset}} |0\rangle \langle 0|$$

(S5)

Here,  $p_Z = (1 - p_{reset})(1 - p_{T1}p_{T2}^{-1})/2$ , and  $p_I = 1 - p_Z - p_{reset}$ . The effect of decoherence on a qubit is expressed via the operator-sum representation, as

$$\rho_{in} \mapsto \mathcal{N}(\rho_{in}) = \rho_{out} = \sum_{k \in I, Z, reset} K_{k_i} \rho_{in} K_{k_i}^{\dagger}$$

(S6)

When  $2T1 \ge T2 > T1$ , the emulators use a Choi-matrix representation of the noise channels (ibm, 2021a,b; Wood, 2020).

## 2 HARDWARE EMULATORS

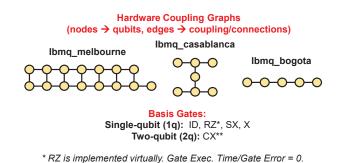

We use three hardware emulators from the Qiskit framework: FakeMelbourne, FakeCasablanca, and FakeBogota (Cross, 2018; ibm, 2021a,b). They emulate the behaviors of the 15-qubit ibmq\_melbourne, 7qubit ibmq\_casablanca, and 5-qubit ibmq\_bogota, respectively (Figure S1). These hardware share the same set of basis/native gates: ID, RZ, SX, X, and CX (CNOT). Each qubit supports the single-qubit operations (ID, RZ, SX, and X). However, the two-qubit CX operations are supported between the connected qubit pairs. Only a subset of all the qubit pairs are connected through couplers. These connections are normally represented by graphs (Figure S1). The nodes denote qubits and the edges denote the couplers. During simulation, the gates in an input circuit are decomposed with the basis/native gates of the hardware. Later, a physical qubit is allocated for every virtual qubit in this circuit. Oftentimes, many of the two-qubit gates in the decomposed circuit can not be executed on hardware due to missing coupling between the allocated physical qubits. SWAP gates are added to the circuit to change the virtual-to-physical qubit mapping dynamically. This change allows some previously inoperable gates to be executed. This whole procedure of converting a circuit for target hardware is often referred to as compilation or transpilation in the literature (Murali et al., 2019; Tannu and Qureshi, 2019; Alam et al., 2020). The quality of the qubits may vary significantly. For example, the error probability of various gates, qubit coherence times, and measurement errors can vary between qubits of the same and different hardware (Table S1). Vendors such

\*\* Two qubit gates are allowed between the connected qubits.

**Figure S1.** Coupling graphs and basis gates of the devices used in this work.

**Table S1.** Summary of the device noise attributes used in this work.

| Attribute       | ibmq_melbourne                     | ibmq_casablanca |                 |       | ibmq_bogota     |                 |  |

|-----------------|------------------------------------|-----------------|-----------------|-------|-----------------|-----------------|--|

|                 | Min   Max   Avg   Std              | Min             | Max   Avg       | Std   | Min   Max       | Avg   Std       |  |

| T1 (us)         | 19.42   105.49   56.07   22.03     | 65.59           | 111.41   89.96  | 15.61 | 85.86   138.54  | 107.56   21.28  |  |

| T2 (us)         | 17.48   102.41   55.49   25.00     | 39.94           | 132.42   85.49  | 36.01 | 72.74   136.19  | 107.03   27.40  |  |

| GET_1q (ns)     | 0.00   142.22   68.57   55.43      | 0.00            | 35.55   26.67   | 15.67 | 0.00   35.55    | 26.67   15.79   |  |

| GET_2q (ns)     | 355.55   1642.67   902.91   313.80 | 305.78          | 497.78   392.29 | 58.07 | 334.22   689.78 | 536.89   130.07 |  |

| GE_1q (%)       | 0.00   0.32   0.10   0.09          | 0.00            | 0.09   0.04     | 0.03  | 0.00   0.10     | 0.03   0.03     |  |

| GE_2q (%)       | 1.47   5.56   3.13   1.13          | 0.75            | 1.83   1.27     | 0.39  | 0.86   7.54     | 2.84   2.93     |  |

| Meas. Error (%) | 2.65   18.66   5.63   3.93         | 1.44            | 3.26   1.89     | 0.63  | 2.71   5.66     | 3.75   1.13     |  |

as, IBM regularly characterize the devices using various protocols (e.g., RB for gate error probability, Hahn Echoes for T2 coherence time, etc.). Many of the calibration data are publicly available (ibm, 2021a). The emulators use this calibration data alongside the compiled circuit to simulate the noisy device behavior using the noise models discussed in the previous section.

Table S1 summarizes the device noise attributes used in this work. We report the minimum, the maximum, the average, and the standard deviation of the following device noise attributes: T1, T2, single-qubit gate execution time (GET\_1q), two-qubit gate execution time (GET\_2q), single-qubit gate error (GE\_1q), two-qubit gate error (GE\_2q), and qubit measurement error (Meas. Error). The ibmq\_melbourne device is the noisiest with the lowest average T1/T2 and the highest average GET\_1q/GET\_2q/GE\_1q/GE\_2q/Meas. Error among the 3. Note that the compilation procedure can have a significant impact on the performance of a quantum circuit (Murali et al., 2019; Tannu and Qureshi, 2019; Ash-Saki et al., 2019; Alam et al., 2020). To ensure fairness in our comparative studies, we use Qiskit's default compilation procedure for all quantum circuits in this work.

#### REFERENCES

[Web] (2021a). Ibm quantum. https://github.com/Qiskit/qiskit-terra/tree/main/qiskit/test/mock/backends [Web] (2021b). Ibm quantum. https://qiskit.org/documentation/tutorials/simulators/

Alam, M., Ash-Saki, A., and Ghosh, S. (2020). Circuit compilation methodologies for quantum approximate optimization algorithm. In 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO) (IEEE), 215–228

Frontiers 3

- Ash-Saki, A., Alam, M., and Ghosh, S. (2019). Qure: Qubit re-allocation in noisy intermediate-scale quantum computers. In *Proceedings of the 56th Annual Design Automation Conference 2019*. 1–6

- Cross, A. (2018). The ibm q experience and qiskit open-source quantum computing software. In *APS March Meeting Abstracts*. vol. 2018, L58–003

- Murali, P., Baker, J. M., Javadi-Abhari, A., Chong, F. T., and Martonosi, M. (2019). Noise-adaptive compiler mappings for noisy intermediate-scale quantum computers. In *Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems*. 1015–1029

- Tannu, S. S. and Qureshi, M. K. (2019). Not all qubits are created equal: a case for variability-aware policies for nisq-era quantum computers. In *Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems*. 987–999

- Wood, C. J. (2020). Special session: Noise characterization and error mitigation in near-term quantum computers. In 2020 IEEE 38th International Conference on Computer Design (ICCD) (IEEE), 13–16