# On Local Activity and Edge of Chaos in a NaMLab Memristor

Alon Ascoli<sup>1,2\*</sup>, Ahmet S. Demirkol<sup>1</sup>, Ronald Tetzlaff<sup>1,2</sup>, Stefan Slesazeck<sup>3</sup>, Thomas Mikolajick<sup>3,4</sup> and Leon O. Chua<sup>5</sup>

<sup>1</sup> Faculty of Electrical and Computer Engineering, Institute of Circuits and Systems, Technische Universität Dresden, Dresden, Germany, <sup>2</sup> Department of Microelectronics, Brno University of Technology, Brno, Czechia, <sup>3</sup> Nano-electronic Materials Laboratory gGmbH, Dresden, Germany, <sup>4</sup> Institute für Halbleiter- und Mikrosystemtechnik, Technische Universität Dresden, Dresden, Germany, <sup>5</sup> Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, Berkeley, CA, United States

#### **OPEN ACCESS**

#### Edited by:

Kyeong-Sik Min, Kookmin University, South Korea

#### Reviewed by:

Guangyi Wang, Hangzhou Dianzi University, China Maheshwar Sah, Tj Maxx, United States Fank Wang, University of Kent, United Kingdom Mauro Forti, University of Siena, Italy

#### \*Correspondence:

Alon Ascoli alon.ascoli@tu-dresden.de

#### Specialty section:

This article was submitted to Neuromorphic Engineering, a section of the journal Frontiers in Neuroscience

Received: 09 January 2021 Accepted: 20 February 2021 Published: 20 April 2021

#### Citation:

Ascoli A, Demirkol AS, Tetzlaff R, Slesazeck S, Mikolajick T and Chua LO (2021) On Local Activity and Edge of Chaos in a NaMLab Memristor.

Front. Neurosci. 15:651452. doi: 10.3389/fnins.2021.651452

Local activity is the capability of a system to amplify infinitesimal fluctuations in energy. Complex phenomena, including the generation of action potentials in neuronal axon membranes, may never emerge in an open system unless some of its constitutive elements operate in a locally active regime. As a result, the recent discovery of solid-state volatile memory devices, which, biased through appropriate DC sources, may enter a local activity domain, and, most importantly, the associated stable yet excitable subdomain, referred to as edge of chaos, which is where the seed of complexity is actually planted, is of great appeal to the neuromorphic engineering community. This paper applies fundamentals from the theory of local activity to an accurate model of a niobium oxide volatile resistance switching memory to derive the conditions necessary to bias the device in the local activity regime. This allows to partition the entire design parameter space into three domains, where the threshold switch is locally passive (LP), locally active but unstable, and both locally active and stable, respectively. The final part of the article is devoted to point out the extent by which the response of the volatile memristor to quasistatic excitations may differ from its dynamics under DC stress. Reporting experimental measurements, which validate the theoretical predictions, this work clearly demonstrates how invaluable is non-linear system theory for the acquirement of a comprehensive picture of the dynamics of highly non-linear devices, which is an essential prerequisite for a conscious and systematic approach to the design of robust neuromorphic electronics. Given that, as recently proved, the potassium and sodium ion channels in biological axon membranes are locally active memristors, the physical realization of novel artificial neural networks, capable to reproduce the functionalities of the human brain more closely than state-of-the-art purely CMOS hardware architectures, should not leave aside the adoption of resistance switching memories, which, under the appropriate provision of energy, are capable to amplify the small signal, such as the niobium dioxide micro-scale device from NaMLab, chosen as object of theoretical and experimental study in this work.

Keywords: memristors, non-linear device modeling, circuit- and system-theoretic methods, theory of non-linear dynamics, local activity theory, physical principle of the edge of chaos

1

#### 1. INTRODUCTION

In recent years, both industry and academia have been devoting efforts toward the exploration of new materials for the fabrication of novel devices, which, combining a number of functionalities within a limited physical volume, may allow the circuit implementation of disruptive computing strategies, allowing to keep the integrated circuit performance (IC) trend predicted by Moore (1965) in the years to come, despite scientists/companies attempting to reduce CMOS transistor dimensions further shall inevitably face a progressive technological/economical failure (Global Foundries Ltd., 2018). In this regard, one of the nanotechnologies with the greatest potential for future electronics (Williams, 2017; Zidan et al., 2018) allows the realization of disruptive circuit elements, known as memoryresistors, or memristors for short (Chua, 1971, 2014, 2015; Chua and Kang, 1976). While the most economically profitable application field of these two-terminal devices is the non-volatile memory sector (Mikolajick et al., 2009; Ielmini and Waser, 2016), their inherently rich dynamical behavior allows to use them alternatively for sensing or processing data. Their peculiar capability to merge a number of different functionalities locally makes them the key nanotechnology enabler toward the future hardware implementation of novel ground-breaking information processing paradigms, including in-memory-computing (Ielmini and Wong, 2018), bio-inspired mem-computing (Di Ventra and Traversa, 2018; Xia and Yang, 2019; Ascoli et al., 2020b,c, 2021; Tetzlaff et al., 2020), and bio-sensing (Tzouvadaki et al., 2016, 2020) strategies.

Moreover, the use of appropriate materials in their fabrication allows to adopt them as basic building blocks of biomimetic neuromorphic circuits (Burr et al., 2015; Yi et al., 2018; Bohaichuk et al., 2019; Fuller et al., 2019; Serb et al., 2020). In this respect, given that the memory and learning capabilities of biological synapses may be rather accurately captured by nonvolatile memristor models (Chua, 2013), and that potassium and sodium ion channels in biological axon membranes essentially are volatile memristors (Ascoli et al., 2020a), as formulated in 1952 from Hodgkin and Huxley in a seminal paper (Hodgkin and Huxley, 1952), for which they were awarded the Nobel Prize in Physiology in 1961, and theoretically proved out in 2012 from Chua in a milestone manuscript (Chua et al., 2012), explaining several paradoxes that arose from their erroneous identification as time-varying resistances, we may conclude that resistance switching memories shall definitely play a fundamental role in the development of bio-realistic hardware implementations of the human brain in the incoming years.

Scientists have already highlighted the capability of certain memristor physical realizations, capable to retain the information stored in their states under zero input, and featuring a finely tunable resistance, to mimic accurately the biological functionalities of synapses (Indiveri et al., 2013). Most importantly, in relation to the research work presented in this paper, other real-world memristors, which fail to store data under no power, but operate excellently as selector devices in non-volatile crossbar memory arrays, allowing to address sneak-path current issues (Zidan et al., 2013), share with the potassium

and sodium ion channels the capability to amplify infinitesimal fluctuations in energy, a fundamental property also referred to as *local activity* (LA) (Mainzer and Chua, 2013), making them ideal candidates to build reliable electronic implementations of spiking neurons.

In order to study the complex dynamics, which volatile memristors, blessed with the capability to enter the locally active regime, and, most importantly, its sub-regime, known as edge of chaos (EOC) (Mainzer and Chua, 2013), where the seed of complexity is actually planted, may induce in circuits, which accommodate them, recurring to the foundations of the LA theory<sup>1</sup> (Chua, 2005) is absolutely necessary<sup>2</sup>. In this regard, the present manuscript employs concepts from the theory of complexity (Mainzer and Chua, 2013) as well as non-linear circuit-centered (Chua, 1987) and system (Ascoli et al., 2019; Corinto et al., 2020) theory-centered methods to analyze an experimentally validated simple yet accurate model of a micro-scale volatile memristor<sup>3</sup> from NaMLab gGmbH (Mähne et al., 2013; Wylezich et al., 2014), allowing us to explain how to stabilize an operating point lying on the negative differential resistance (NDR) region of the device DC current-voltage characteristic, and to draw a comprehensive picture of the possible operating modes of the microstructure. It is instructive to observe that gaining a complete understanding of the non-linear dynamics of particular miniaturized resistance switching memories, which are capable to amplify the small signal superimposed on top of an appropriate bias level, e.g., those realized by Hewlett Packard (Pickett and Williams, 2012) or the ones manufactured at the NaMLab facilities and investigated in this manuscript, is a fundamental pre-requirement toward the future development of a systematic and conscious approach to design bio-inspired spiking neural networks, which, employing memristive electronic implementations of biological neurons (Pickett et al., 2013), are expected to reproduce the extraordinarily rich panorama of computing functionalities of the human brain (Pickett and Williams, 2013) beyond the current capabilities of traditional purely CMOS hardware (Chicca et al., 2014).

This article holds a strong pedagogical role, providing a legacy of theoretical knowledge to the next generation of scientists interested in the design of neuromorphic electronics. To the best of our knowledge, this is the very first time that the application of circuit and system-theoretic methods, supported by experimental validation, allows to draw a complete classification of all the admissible operating domains of a memristor, namely the LP, the LA, and the EOC regimes, under both voltage and current control. Importantly, this work paves the way toward the development of a novel systematic neuromorphic hardware design approach, in

<sup>&</sup>lt;sup>1</sup>A novel interesting perspective to interpret concepts from the LA theory has been recently provided in Garay (2017).

<sup>&</sup>lt;sup>2</sup>The literature holds a number of impressive works, in which methods from the LA theory have been adopted to explain complexity in systems from disparate fields, including biology (Dogaru and Chua, 1998) and electronics (Min and Chen, 2004).

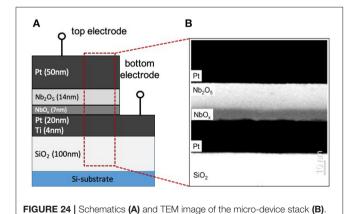

<sup>&</sup>lt;sup>3</sup>An **Appendix** at the end of the paper provides a brief overview on the fabrication, material composition, geometric structure, and physics of the threshold switch under study.

which variability-tolerant measures may be consciously taken to prevent its basic components from exiting safe operating modes.

In regard to the structure of the article, section 2 explores the DC behavior of the voltage-controlled volatile memristor from NaMLab, identifying the conditions that allow to bias the micro-scale device along the NDR region of its DC characteristic, where it is said to operate in the locally active regime. Section 3 introduces a rigorous discussion on the device LA, namely its capability to amplify infinitesimal fluctuations in energy, on the basis of the analysis of its small-signal equivalent circuit model, identifying also the conditions under which the NbO memristor may enter the "pearl" (Chua, 2005) embedded in the LA domain, namely the EOC, and, providing, finally, a complete classification of all the possible operating regimes of the threshold switch. Importantly, on the basis of concordant experimental measurements and model predictions, section 4 clarifies once and for all when and how does the response of the threshold switch to quasi-static stimuli differs from its DC behavior. A brief discussion, pinpointing the significance of this research work for the future development of a systematic method to design artificial neural networks capable to operate according to the same mem-computing principles lying at the basis of the human brain information processing paradigm, is provided in section 5. Conclusions are finally drafted in section 6. An Appendix with supplementary information on the microstructure under our magnifying glass in this work is provided in section 6.

### 2. EXPLORATION OF LA AND EOC IN AN **NBO VOLATILE MEMRISTOR**

The next section introduces a purely mathematical yet accurate model of a micro-scale niobium oxide (NbO) volatile memristor manufactured at NaMLab gGmbH (Mähne et al., 2013; Wylezich et al., 2014). Under the time invariance assumption<sup>4</sup>, each twoterminal circuit element from the class of voltage-controlled extended memristors is defined via the following differential algebraic equation (DAE) set<sup>5</sup> (Chua, 2018):

$$\frac{d\mathbf{x}}{dt} = \mathbf{g}(\mathbf{x}, \nu_m),\tag{1}$$

$$i_m = G(\mathbf{x}, \nu_m) \cdot \nu_m, \tag{2}$$

where  $v_m$  ( $i_m$ ) stands for the voltage (current) falling across (flowing through) the one-port<sup>6</sup>,  $\mathbf{x} \triangleq [x_1, x_2, \dots, x_k]^{\mathsf{T}} \in \mathbb{R}^k$ denotes in general a k-dimensional memory state<sup>7</sup>, while both state evolution function  $\mathbf{g}(\cdot,\cdot):\mathbb{R}^k\times\mathbb{R}\to\mathbb{R}^k$  and memductance function  $G(\cdot,\cdot):\mathbb{R}^k\times\mathbb{R}\to\mathbb{R}$  depend upon state and input variables. Importantly, the inequality  $G(\mathbf{x},0) \neq \infty$  must hold true, i.e., the memductance function has to be finite for zero voltage in order for the model of an extended memristor to capture its coincident zero-crossing signature, which establishes that the output of the device always crosses the time axis at the same instants as its input<sup>8</sup>.

In case the memductance function is independent of the voltage stimulus, the DAE set (1) and (2) reduces to

$$\frac{d\mathbf{x}}{dt} = \mathbf{g}(\mathbf{x}, \nu_m),$$

$$i_m = G(\mathbf{x}) \cdot \nu_m,$$

(3)

$$i_m = G(\mathbf{x}) \cdot \nu_m, \tag{4}$$

and the one-port is said to belong to the class of voltage-controlled generic memristors.

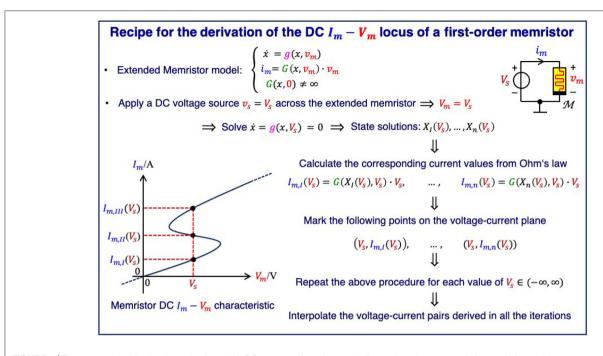

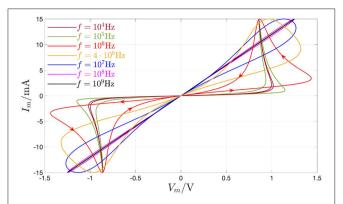

Figure 1 illustrates the steps necessary to derive the DC current-voltage locus of a first-order voltage-controlled extended memristor<sup>9</sup> (Chua, 2014) systematically. It is worth to pinpoint that, actually, this rigorous procedure is never carried out in the lab. In fact, among experimentalists, it is common practice to perform quasi-DC tests (Chua, 2015), also referred to as quasistatic measurements, to characterize the DC current (voltage) response of a voltage (current)-controlled memristor. However, as will be clarified in section 4, extra care should be taken in the selection of the kind of excitation stimulus, i.e., a voltage or a current source, to use for the quasi-static test on a device sample in order to measure a close approximation to its DC characteristic.

### 2.1. Application of a Non-linear System Identification Technique for Modeling a **NbO Volatile Memristor**

The Unfolding Theorem<sup>10</sup> (Chua, 2011) defines a non-linear system identification method, which allows to determine a purely mathematical description of a memristor device in the voltage-current domain on the basis of a set of experimental data, without requiring a preliminary understanding of the physical mechanisms underlying the device operating principles. Applying this theorem, under low current operation<sup>11</sup> the

<sup>&</sup>lt;sup>4</sup>A circuit element is said to be *time invariant* if its input-output behavior does not change over time.

<sup>&</sup>lt;sup>5</sup>The model of a current-controlled extended memristor may be derived mutatis mutandis from Equations (1) and (2) by invoking the duality principle (Chua,

$<sup>^6{\</sup>rm The\ memristor\ voltage}\ \nu_m$  (current  $i_m)$  is also referred to as the input or control (output) variable of a voltage-controlled memristor. By the duality principle (Chua, 1987), a similar nomenclature may be adopted mutatis mutandis for a current-controlled memristor.

<sup>&</sup>lt;sup>7</sup>The memory state vector  $\mathbf{x}$  of a volatile memristor is unable to store information, not even in digital binary form, for zero input. Therefore, precisely, it should be interpreted as a volatile memory state.

<sup>&</sup>lt;sup>8</sup>If the constraint  $G(\mathbf{x},0) \neq \infty$  were not included in the definition of an extended memristor, the DAE set (1) and (2) could be used to model other dynamic circuit elements, e.g., linear capacitors and inductors (Chua, 2014).

<sup>&</sup>lt;sup>9</sup>Invoking the duality principle (Chua, 1987) a similar recipe may be written down mutatis mutandis for the determination of the DC voltage-current characteristic of a first-order current-controlled extended memristor.

$<sup>^{10}</sup>$ Referring to a first-order voltage-controlled extended memristor, the UnfoldingTheorem (Chua, 2011) envisages the expansion of the state evolution function  $g(\mathbf{x}, \nu_m)$  in Equation (1) and of the memductance function  $G(\mathbf{x}, \nu_m)$  in Equation (2), for  $\mathbf{x} = x$ , into sums and products of polynomial series in input and state variables

<sup>&</sup>lt;sup>11</sup>Keeping the maximum current flowing through the device below an upper bound of about 15 mA, the threshold switching dynamics emerging in the NbO micro-film are not found to be accompanied by non-volatile memory effects. However, if higher currents are let flow through the device, the latter is found to feature distinct resistive levels for no input (Mähne et al., 2013) besides maintaining an abrupt switching behavior upon excitation. For modeling the NbO memristor accurately under these circumstances, the dynamic law of another non-volatile memory state needs to be specified (Slesazeck et al., 2016). Since the device was operated in the low current regime during all the experimental investigations associated to this research, a volatile memristor model is adopted

FIGURE 1 | Rigorous method for the determination of the DC current-voltage locus of a first-order voltage-controlled extended memristor.

non-linear dynamics of a micro-scale NbO volatile resistance switching memory from NaMlab was found to be captured accurately by a voltage-controlled generic memristor model, reading as the DAE set (3) and (4), where the state evolution and memductance functions are respectively, expressed by

$$g(x, v_m) = a_0 + a_1 \cdot x + (b_2 + c_{21} \cdot x + c_{22} \cdot x^2 + c_{23} \cdot x^3 + c_{24} \cdot x^4 + c_{25} \cdot x^5) \cdot v_m^2, \text{ and}$$

(5)

$$G(x) = d_0 + d_1 \cdot x + d_2 \cdot x^2 + d_3 \cdot x^3 + d_4 \cdot x^4, \tag{6}$$

in which the coefficient values, tuned through a standard optimization procedure, are reported in **Table 1**.

## 2.2. DRM- and Circuit-Theoretic Based Investigations of the Device DC Response

Following the iterative procedure given in **Figure 1**, the voltage  $V_s$  of a hypothetical DC source, inserted in parallel to the NbO device, is varied in small steps from 0 V to 1.046 V, and, for each value of the voltage  $V_m = V_s$ , which consequently falls across the memristor<sup>12</sup>, the following operations are executed.

• All the possible zeros  $X_I$ ,  $X_{II}$ , . . ., and  $X_n$  of the associated state evolution function  $g(x, V_s)$  in Equation (5) are first calculated.

in this manuscript to capture the dynamics of the NbO threshold switch. However, for pedagogical reasons, and for the sake of completeness, some of the theoretical results, descending from the analysis of this model, e.g., the device DC current-voltage characteristic, shall cover also the high current regime.

**TABLE 1** Values assigned to the coefficients of the polynomial series developments of state evolution function (5) and memductance function (6) in the proposed NbO micro-device model (3) and (4).

| $a_0$ 5.19 · 10 <sup>9</sup>  | $a_1$ $-2.05 \cdot 10^7$         | <i>b</i> <sub>2</sub> 7.21 · 10 <sup>9</sup> | $c_{21}$ $-0.07 \cdot 10^9$   | c <sub>22</sub><br>2.27 · 10 <sup>5</sup> |

|-------------------------------|----------------------------------|----------------------------------------------|-------------------------------|-------------------------------------------|

| $c_{23}$ $-2.40 \cdot 10^2$   | $c_{24}$ 1.25 · 10 <sup>-1</sup> | $c_{25}$ $-2.69 \cdot 10^{-5}$               | $d_0$ 6.50 · 10 <sup>-3</sup> | $d_1$ $-6.66 \cdot 10^{-5}$               |

| $d_2$ 2.14 · 10 <sup>-7</sup> | $d_3$ $-2.14 \cdot 10^{-10}$     |                                              |                               | $d_4$ 1.19 · 10 <sup>-13</sup>            |

A voltage-controlled memristor DAE set (1) and (2), adapted to the first-order case, and with  $g(x,v_m)$  and  $G(x,v_m)$  expressed as sums and products of polynomial series in input and state variables, was chosen as model template. Adopting a bottom-up approach, a standard optimization procedure was set in place to massage the coefficients of the simplest possible form of the polynomial-based model template so as to decrease the cumulative Relative Root Mean Quadratic Error (RRMQE) between a multivariate set of experimental data extracted from a device sample and the corresponding model predictions below a predefined threshold. The complexity of the two series expansions was progressively increased after ensuring that any possible simpler model would fail to meet the objective of the optimization procedure. As compared to the parameter setting, tabulated in Ascoli et al. (2015), where the proposed model was originally formulated, an additional fine tuning of the real coefficients in the polynomial series expansions of  $g(x,v_m)$  and  $G(x,v_m)$  was carried out so as to fit the DAE set to experimental data extracted from a different NbO micro-scale device sample.

- The *n* memory state DC values are then inserted into Ohm's law (4) to obtain the associated currents  $I_{m,I} = G(X_I) \cdot V_s$ ,  $I_{m,II} = G(X_{II}) \cdot V_s$ , ..., and  $I_{m,n} = G(X_n) \cdot V_s$ , where the memductance function is expressed by Equation (6).

- The *n* DC voltage-current pairs  $(V_s, I_{m,I})$ ,  $(V_s, I_{m,II})$ , ..., and  $(V_s, I_{m,n})$  are subsequently plotted on the voltage-current plane.

$<sup>^{12}</sup>V_m$ , X, and  $I_m$  denote the DC values for memristor voltage, state, and current, respectively. The triplet  $(V_m, X, I_m)$  defines a DC operating point for the memristor.

Interpolating all the points, obtained through the entire cycle of iterations, delivers, finally, the DC characteristic of the microscale device.

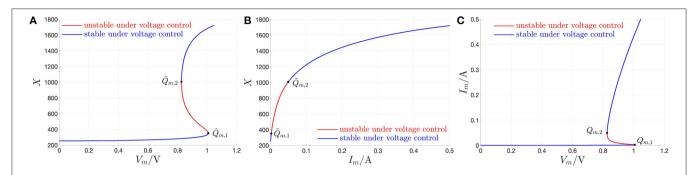

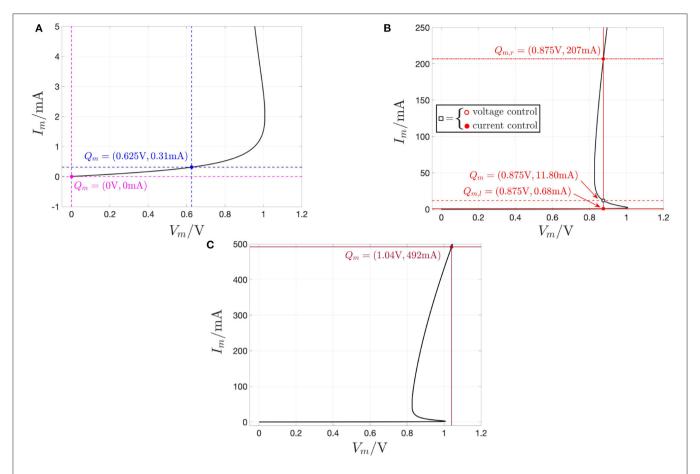

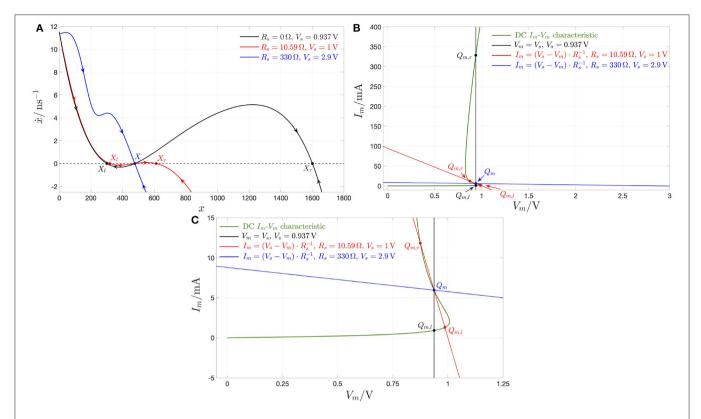

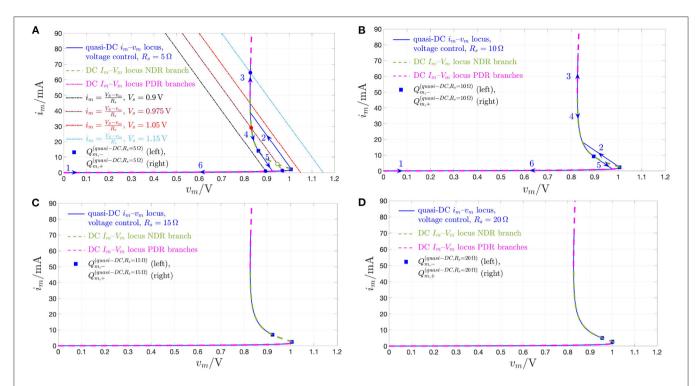

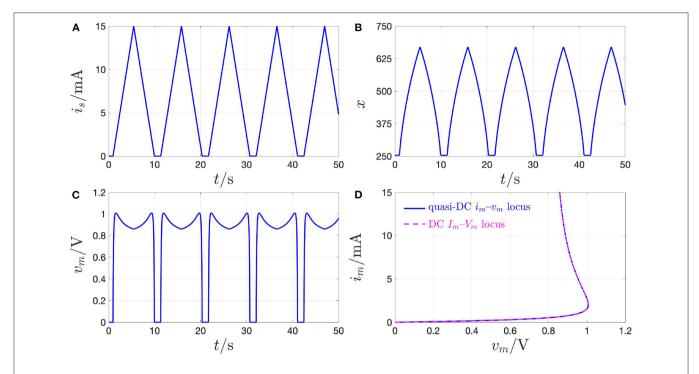

**Figure 2A** shows all the possible DC operating points of the memristor state, i.e., all the *X*-values, at which the state equation (3), with state evolution function (5), vanishes, for each  $V_m$  value. Correspondingly, using Ohm's law (4), with memductance function (6), the locus of the memory state DC operating point *X* vs. the device DC current  $I_m$  is found to be illustrated by **Figure 2B**. Importantly, *X* is a multi (single)-valued function of the memristor DC voltage (current) for  $V_m \in [V_{m,a}, V_{m,b}] = [0 \text{ V}, 1.046 \text{ V}]$  ( $I_m \in [I_{m,a}, I_{m,b}] = [0 \text{ A}, 500 \text{ mA}]$ ), assuming values in the set<sup>13</sup>  $[X_a, X_b] = [253, 1722]$ . Finally, with reference to **Figure 2**, on the basis of plots (A) and (B), for each memristor DC voltage value, all the possible DC currents, which may flow through the two-terminal circuit element, are displayed in plot (C), which represents the DC  $I_m$ - $V_m$  characteristic<sup>14</sup> of the threshold switch from NaMLab.

REMARK 1. Interestingly, the same results visualized in Figure 2 may be obtained by applying the variant of the recipe in Figure 1, applicable to current-controlled extended memristors, to the current-driven version of the proposed NbO device model DAE set (3) and (4) with  $g(x, v_m)$  and G(x) expressed by Equations (5) and (6), respectively, i.e., to the current-controlled generic memristor DAE set

$$\frac{d\mathbf{x}}{dt} = f(\mathbf{x}, i_m),\tag{7}$$

$$v_m = R(\mathbf{x}) \cdot i_m, \tag{8}$$

where  $\mathbf{f}(\cdot, \cdot): \mathbb{R}^n \times \mathbb{R} \to \mathbb{R}^n$ , denoting the state evolution function, and  $R(\cdot): \mathbb{R}^n \to \mathbb{R}$ , standing for the memristance function, are respectively, expressed as

$$f(x, i_m) = g(x, G^{-1}(x) \cdot i_m), and$$

(9)

$$R(x) = G^{-1}(x), (10)$$

and sweeping the memristor DC current  $I_m$  within the range<sup>15</sup>  $[I_{m,a}, I_{m,b}] = [0, 500 \text{ mA}].$

Calculating the slope of the DC current-voltage locus at each point, which lies along it, the *small-signal or differential or local*

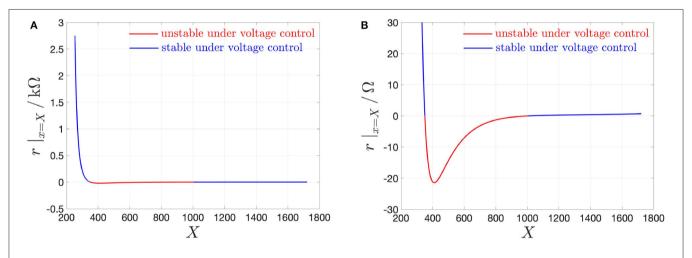

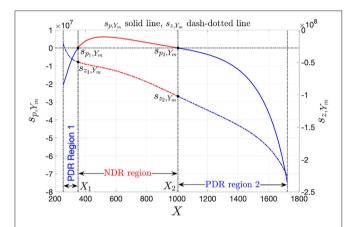

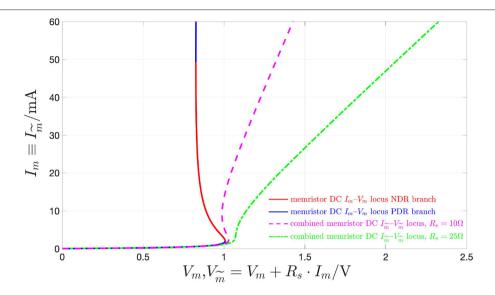

resistance  $r|_{v_m=V_m} \triangleq \left(\frac{di_m}{dv_m}|_{v_m=V_m}\right)^{-1}$  is found to be negative for  $V_m \in (V_{m,2}, V_{m,1}) = (0.826, 1.007)$  V, and, correspondingly, for  $X \in (X_1, X_2) = (351, 1006)$ , and for  $I_m \in (I_{m,1}, I_{m,2}) = (2.037, 49.296)$  mA. **Figure 3A** depicts the NbO device small-signal resistance r vs. the memory state DC operating point X.

The range of *X*-values ( $X_1$ ,  $X_2$ ) = (351, 1,006), where  $r < 0 \Omega$ , defines the *negative differential resistance* (NDR) region of the DC  $I_m$ - $V_m$  characteristic of the micro-scale threshold switch (**Figure 3B**). The range of *X*-values [ $X_a$ ,  $X_1$ ) = [253, 351) (( $X_2$ ,  $X_b$  = [1,006, 1,722]), where  $r > 0 \Omega$ , defines the lower (upper) *positive differential resistance* (PDR) region of the DC  $I_m$ - $V_m$  characteristic of the micro-scale threshold switch<sup>16</sup>.

REMARK 2. The values of the memristor state in the proposed model reveal an association between x and the device internal temperature T. On the basis of this assumption, given that the memristor state X range along the NDR region, specifically  $(X_1, X_2) = (351, 1,006)$ , indicates that the threshold switch does not attain the NbO Mott phase transition temperature of  $T_{Mott} = 1,050$  K throughout the operating mode where it features a small-signal conductance of negative polarity. This conjecture, examined in Slesazeck et al. (2015), was recently adopted and confirmed in other prominent scientific studies (Gibson et al., 2016; Kumar et al., 2017).

A deeper understanding of the device non-linear behavior may be inferred by studying its *dynamic route map* (DRM) (Chua, 2018), a powerful graphical tool for the analysis of first-order dynamical systems<sup>17</sup>.

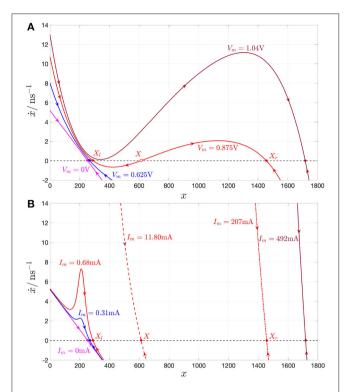

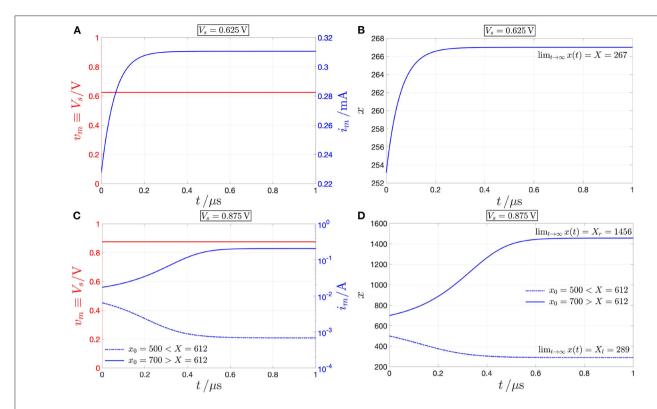

**Figure 4A** depicts the NbO device *state dynamic routes* (SDRs) for each value of the memristor DC voltage  $V_m$  in the set  $S_{V_m} \triangleq \{0, 0.625, 0.875, 1.04\}$  V. As  $V_m$  is progressively

<sup>&</sup>lt;sup>13</sup>Setting to 0 the state evolution function (5) for  $V_m = V_{m,a} = 0$  V, the formula for the unique memristor state equilibrium is easily found to be  $X_a = X(V_{m,a}) = X(V_m = 0 \text{ V}) = -a_0/a_1 = 253.15$ .

<sup>&</sup>lt;sup>14</sup>In this article, the abscissa and ordinate of a generic operating point  $Q_{m,i}$  –  $i \in \{I, II, \ldots\}$  – along the device DC  $I_m$ – $V_m$  characteristic are denoted as  $V_{m,i}$  and  $I_{m,i}$ , respectively.

<sup>&</sup>lt;sup>15</sup>This approach is simpler than the one assuming a voltage control, since, here, the "dual" recipe of the procedure illustrated in **Figure 1**, applicable to any current-driven extended memristor model, would require the numerical calculation of a single zero for the state evolution function (9) for each DC value  $I_m$  assigned to the memristor current  $i_m$  (as may be inferred from **Figure 2B**, X is a single-valued function of  $I_m$ ). Importantly, under current sweep, each memristor state DC operating point X is found to be *globally asymptotically stable*, as will be discussed in more depth shortly (see **Figure 2B** for more details). As a result, according to the color coding convention adopted in **Figure 2**, all the points in the loci from plots (A–C) should be marked in blue under current control.

$<sup>^{16}</sup>$ In **Figure 12**, the lower (upper) PDR branch of the device DC  $I_m$ – $V_m$  locus will be referred to as PDR region 1 (2).

<sup>&</sup>lt;sup>17</sup>Let a first-order dynamical system be described by a non-linear ODE of the form  $\dot{x} = f(x, \mu)$ , where  $x \in \mathbb{R}$  denotes the state variable,  $\mu \in \mathbb{R}$  stands for a control parameter, and  $f(\cdot, \cdot) : \mathbb{R} \times \mathbb{R} \to \mathbb{R}$  defines the state evolution function. Plotting the time derivative  $\dot{x}$  of the state variable vs. the state variable itself for a specific value  $\bar{\mu}$  of the control parameters  $\mu$ , and endowing the resulting locus with arrows pointing toward the east (west) on the positive (negative) half plane, provides a state dynamic route (SDR), illustrating the path, which x follows from any initial condition  $x_0 \triangleq x(0)$  in this scenario. An ODE equilibrium  $\bar{x}$  for  $\mu = \bar{\mu}$ corresponds to a state, which lies along the horizontal axis on the  $f(x, \bar{\mu})$  vs. x locus ( $\dot{x}$  vanishes at its location), and is said to be asymptotically stable (to be unstable) if the SDR features a negative (positive) slope therein, implying that, perturbing the system slightly away from its position, the system solution moves back to (departs from) it as time proceeds. The dynamic route map (DRM) of the first-order system is a family of SDRs, one for each of the admissible values of the control parameter  $\mu$ . Importantly, X is the symbol adopted in this article to denote a zero of the memristor state evolution function in Equations (5) and (9), namely  $g(x, v_m)$   $(f(x, i_m) = g(x, R(x) \cdot i_m), \text{ with } R(x) = G^{-1}(x), \text{ as established})$ by Equation (10), and G(x) expressed by formula (6)) under a given DC  $V_m$  ( $I_m$ ) value. X, referred to as an equilibrium for the memristor state Equations (3) and (7), with state evolution function expressed by formula (5) and (9), under the specified bias voltage (current) stimulus  $V_m$  ( $I_m$ ), indicates a possible DC operating point for the memristor state in this scenario. Finally, it is worth mentioning that, recently, the DRM graphical tool has been extended to nonlinear dynamical systems with two degrees of freedom (Tetzlaff et al., 2020), which shall allow, for example, an in-depth study of the nonlinear dynamics of second-order memristors.

**FIGURE 2** | Application of the recipe shown in **Figure 1** to obtain the DC  $I_m$  vs.  $V_m$  locus of the NbO memristor through a voltage sweep. **(A,B)** Any possible zero X of the state evolution function  $g(x, v_m)$  for each DC value  $V_m$  of the memristor voltage  $v_m$  from a set of equally spaced points chosen within the range  $[V_{m,a}, V_{m,b}] = [0 \, V_m, 0.046 \, V_m]$ , vs.  $V_m$  ( $I_m = G(X) \cdot V_m$ ). The X- and  $I_m$ -ranges are  $[X_a, X_b] = [253, 1722]$  and  $[I_{m,a}, I_{m,b}] = [0 \, A, 500 \, \text{mA}]$ , respectively. **(C)** DC  $I_m$  vs.  $V_m$  locus obtained by plotting any admissible pair  $(V_m, I_m) = G(X) \cdot V_m$ ) inferrable from **(A,B)**. As explained in detail in the text, each point  $(V_m, I_m)$ , lying on the NDR region of the DC current-voltage characteristic, obtained under voltage sweep, is found to be unstable. The red and blue colors in **(A-C)** highlight unstable and stable DC operating points of the memristor under voltage control, respectively. The unstable X-range is  $[X_1, X_2] = [351, 1006]$ . Correspondingly, the memristor voltage and current, respectively, lie within the ranges  $V_m \in [V_{m,2}, V_{m,1}] = [0.826 \, V, 1.007 \, V]$ , and  $I_m \in [I_{m,1}, I_{m,2}] = [2.037 \, \text{mA}, 49.296 \, \text{mA}]$ . The points  $\hat{Q}_{m,1} = (V_{m,1}, X_1)$  and  $\hat{Q}_{m,2} = (V_{m,2}, X_2)$ , respectively located at the lower and upper bound of the NDR region in the  $V_m - X$  plane, are shown in **(A)**. The corresponding pair of points in the  $I_m - X$  ( $V_m - I_m$ ) plane, namely  $\hat{Q}_{m,1} = (I_{m,1}, X_1)$  and  $\hat{Q}_{m,2} = (V_{m,2}, I_{m,2})$ , are shown in **(B,C)**.

FIGURE 3 | (A) Small-signal resistance r |<sub>x=X</sub> of the NbO memristor vs. memory state DC operating point X. In red (blue), the NDR (PDR) values, which, as revealed in the text, are associated to unstable (stable) memory state DC operating points for the voltage-driven memristor device. (B) Close-up view on the NDR region, identifiable on the horizontal axis for each X-value within the range [351, 1006]. Note that  $\hat{r}$ , defined in Equation (16), and denoting the largest modulus of the device small-signal resistance in the NDR region, appears at X = 411, and is equal to 21.43 Ω. Another state bias point of significance for the remainder of this manuscript is X = 478, where r is found to be equal to  $-16.514 \Omega$ .

increased within this set, for the first zero input scenario the voltage-driven memristor exhibits a globally asymptotically stable state operating point. The locus of  $\dot{x}$  vs. x under no input, known as power-off plot (POP) (Chua, 2015) and depicted in pink in plot (A), crosses in fact the state axis in a single point, namely  $X = -\frac{a_0}{a_1} = 253.15$ , with negative slope, confirming that, as anticipated earlier, the micro-scale device from NaMLab is a volatile memory under the relatively low current range under focus. The blue SDR, resulting upon the assignment of the second DC value in the set  $S_{V_m}$  to  $V_m$ , also crosses once and with negative slope the state axis, specifically in X = 267, and, correspondingly, the memristor keeps its monostable character in this case. As the DC input is further increased, the memristive system loses monostability, acquiring the capability to evolve toward one of

two possible operating points. For  $V_m=0.875\,\mathrm{V}$ , the SDR, drawn in red in plot (A), crosses the memory state axis in three points, specifically  $X_l=289,~X=612,~\mathrm{and}~X_r=1,456,~\mathrm{of}$  which each of the outer ones (of which the center one) are locally stable (is unstable), given that  $\frac{dx}{dx}\big|_{V_m=0.875\,\mathrm{V}}$  is negative (positive) therein. Increasing the DC input further, the device undergoes a reverse bifurcation from bistability back to monostability. For the last  $V_m$ -value in  $S_{V_m}$ , the SDR, illustrated in brown in plot (A), admits once again a negative slope in the single location, where it crosses the horizontal axis, namely in  $X=1,725,~\mathrm{and},~\mathrm{as}$  a result, the memristor exhibits one and only one globally asymptotically stable operating point.

Thus, the memristor SDR, resulting upon assigning the first, second, and fourth values (the third value) in

**FIGURE 4 | (A)** DRM of the NbO memristor under voltage control for each  $V_m$ value in the set  $S_{V_m} \triangleq \{0, 0.625, 0.875, 1.04\} \text{V.}$  (B) DRM of the NbO memristor under current control for each  $I_m$  value in the set  $S_{l_m} \triangleq \{0, 0.31, 0.68, 11.80, 207, 492\}$ mA. Analyzing the  $V_m$  range [0 V, 1.046 V], shown in the DC  $I_m$ - $V_m$  characteristic of **Figure 2C**, the device exhibits a monostable character, except for  $V_m \in [0.826, 1.007V]$ , where it is found to feature bistability. On the other hand, for each DC current  $I_m$  value in the range [0, 500 mA] from **Figure 2C**, the memristor keeps monostability. In both plots a hollow (filled) circle on the horizontal axis indicates an unstable (a stable) memristor state DC operating point X under a given DC input. The pink-colored POP of the device under either voltage or current control crosses the state axis with negative slope at  $X = -\frac{a_0}{a_1} = 253.15$ , clearly classifying the NbO memristor as a volatile memory according to the proposed model. Also for  $V_m = 0.625 \,\text{V}$ , or, alternatively, for  $I_m = 0.31 \,\text{mA}$  (for  $V_m = 1.04 \,\text{V}$ , or, alternatively, for  $I_m = 492 \,\text{mA}$ ), the blue (brown) SDR under voltage, or, alternatively, current control, admits a single intersection with the state axis, namely X = 267 (X = 1725), and negative slope therein. For  $V_m = 0.875$  V, the device features three possible equilibria, namely  $X_1 = 289$ , X = 612, and  $X_c = 1456$ , of which only the outer ones are stable, as may be inferred from (A). The memristor may asymptotically attain the first, second, and third operating point in this triplet by letting a specific DC current, equal to 0.68, 11.80, and 207 mA, respectively, flow through the device, as revealed by the red SDR in solid, dashed, and dash-dotted line style in (B).

the set  $S_{V_m}$  to the device DC voltage  $V_m$ , admits the first, second, and sixth value (the third, fourth, and fifth values) for the memristor state operating point X in the set  $S_X \in \{253, 267, 289, 612, 1, 456, 1, 725\}$ . From Ohm's law—refer to Equations (4)–(6)—or using directly the data associated with the device DC current-voltage locus in **Figure 2C**, it may be evinced that the memristor may attain the kth equilibrium in the set  $S_X$  also upon letting a DC current of value equal to the kth number in the set  $S_{I_m} \triangleq \{0, 0.31, 0.68, 11.80, 207, 492\}$  mA flow across the device ( $k \in \{1, 2, 3, 4, 5, 6\}$ ). **Figure 4B** depicts

the locus of the state evolution function (5), with memristor voltage expressed as  $v_m = G^{-1}(x) \cdot i_m$ , for each DC value  $i_m = I_m$  in  $S_{I_m}$ . With reference to **Figure 4**, the SDR (all the SDRs), appearing in plot (B), and, respectively, associated with the first, second, and sixth value (respectively, associated with the third, fourth, and fifth values) of the memristor DC current  $I_m$  in  $S_{I_m}$  is in turn drawn in pink, blue, and brown (are drawn in red), as the SDR, which admits the same equilibrium (admits each of their three distinct equilibria) under voltage control, i.e., the one shown in plot (A), and obtained upon assigning the first, second, and fourth (assigning the third) value in the set  $S_{V_m}$  to the memristor DC voltage  $V_m$ . Remarkably, each of the memristor SDRs, corresponding to values of the device DC current  $I_m$  in the set  $S_{I_m}$ , admits one and only one intersection with the horizontal axis, crossing it with a negative slope, which demonstrates the robust nature of the monostability of the device under current control.

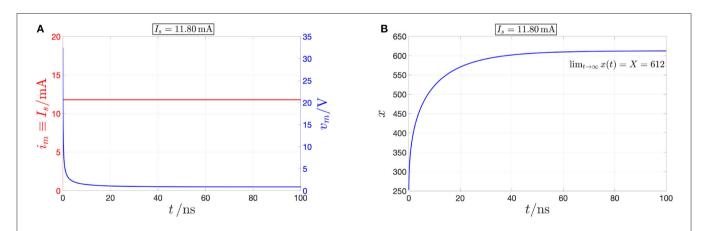

REMARK 3. A deeper understanding may be gained by analyzing the memristor DC response from a circuit-theoretic perspective. The load line corresponding to the scenario, where a voltage (current) source  $V_s$  ( $I_s$ ) is applied directly across the NbO threshold switch, corresponds to a vertical (horizontal) linear locus of equation  $V_m = V_s$  ( $I_m = I_s$ ) in the voltage-current plane. Under voltage (current) control, each intersection  $Q_m = (V_m = V_s, I_m)$  $(Q_m = (V_m, I_m = I_s))$  between the vertical (horizontal) load line and the memristor DC  $I_m$ - $V_m$  characteristic is a possible operating point for the device. With reference to Figure 5, for each  $V_s$  value in the set  $\{0, 0.625\}$  V (for  $V_s = 1.04$  V) the memristor admits a unique operating point  $Q_m$ , with coordinates reported in plots (A) and (C), and with a globally asymptotically stable character, as clear from the analysis of the respective SDR in Figure 4A. For example, stressing the device with a DC voltage of value  $V_s = 0.625 \text{ V}$ , as shown through a red color in Figure 6A, the threshold switch may be polarized in one and only one globally asymptotically stable operating point, which lies on the lower PDR of its DC  $I_m$ - $V_m$  characteristic, specifically at  $Q_m =$  $(V_m, I_m) = (0.625 \text{ V}, 0.31 \text{ mA})$ , as expected from Figure 5A, and demonstrated through a numerical simulation of the proposed polynomial-based model (see Figures 6A,B, depicting in blue the time evolution of memristor current and state, respectively).

However, as illustrated in **Figure 5B**, for  $V_s = 0.875$  V, three are the voltage-current pairs, at which the device DC characteristic crosses the respective vertical load line, i.e.,  $Q_{m,l}$ ,  $Q_m$ , and  $Q_{m,r}$ , of which the one (the two) lying on (outside of) the NDR region of the DC  $I_m$ - $V_m$  locus is unstable (are locally asymptotically stable), as established through the investigation of the respective SDR in **Figure 4A**. Stimulating the NbO threshold switch by means of a source of DC voltage  $V_s = 0.875$  V, as shown in red in **Figure 6C**, a couple of numerical simulations of the proposed unfolding theorem-based model provide evidence for the threshold switch bistability. Setting the initial memristor state  $x_0$  below (above) the unstable point X = 612, the device may be polarized in a locally asymptotically stable operating point lying on the lower (upper) PDR branch of its DC  $I_m$ - $V_m$  characteristic, in particular at  $Q_{m,l} = (0.875 \text{ V}, 0.68 \text{ mA})$   $[Q_{m,r} = (0.875 \text{ V}, 207 \text{ mA})]$ ,

as expected from **Figure 5B**, and illustrated in **Figures 6C,D**, depicting in blue and with a dash-dotted (solid) linestyle the approach of memristor current and state to the lower (upper) bias solution from the admissible stable pair, respectively.

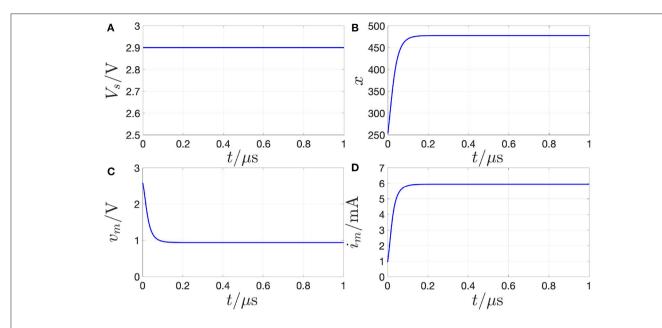

On the contrary, referring once more to **Figure 5**, for each  $I_s$ value in  $S_{I_m}$ —see plots (A), (B), and (C) for  $I_s \in \{0, 0.31\}$  mA, for  $I_s \in \{0.68, 11.80, 207, \} mA$ , and for  $I_s = 462 mA$ , respectively the device is found to possess one and only one operating point  $Q_m$ , which is globally asymptotically stable, as determined earlier on through the study of the respective current-driven memristor SDRs shown in Figure 4B. Applying a source of DC current  $I_s = 11.80 \, mA$  directly across the threshold switch, as shown in red in Figure 7A, a numerical simulation of the polynomial-based model demonstrates the global asymptotic stability of the operating point  $Q_m = (V_m, I_m) = (0.875 \text{ V}, 11.80 \text{ mA})$ , lying on the NDR branch of the device DC characteristic. Setting the initial condition  $x_0$  arbitrarily to 253.15, the device is indeed found to converge asymptotically toward this NDR bias point, as expected from Figure 5B, and visualized in Figures 7A,B, where the memristor voltage (state) is found to approach the value  $V_m = 0.875 V$ (X = 612) as time goes to  $\infty$ .

### 2.3. NDR Stabilization Under Voltage Control

The analysis of section 2.2 has revealed that the memristor may be biased in any point of the NDR region of its DC  $I_m$ - $V_m$  locus by letting a suitable DC current flow through it. On the other hand, the entire NDR region of the memristor DC current-voltage characteristic is unstable under voltage control. This notwithstanding, it is possible to stabilize any point along the NDR domain by inserting a linear resistor  $R_s$  of appropriate resistance between the DC voltage source  $V_s$  and the memristor, as shown in Figure 8A. This section explains how to tune the parameters of the biasing circuit in this figure for the stabilization of a given NDR operating point  $Q_m = (V_m, I_m)$  on the memristor DC  $I_m$ - $V_m$  characteristic<sup>18</sup>. An example shall be used to illustrate this concept. Suppose it is desirable to stabilize the memristor state equilibrium X = 478, i.e., equivalently, the corresponding operating point  $Q_m = (0.937 \text{ V}, 5.948 \text{ mA})$  on the device DC characteristic. Let us select the parameters  $V_s$  and  $R_s$  of the biasing circuit in three distinct ways, and analyze the resulting scenarios. First, applying a DC voltage of value  $V_s = 0.937 \,\mathrm{V}$ directly across the threshold switch, i.e., without introducing a series resistor in Figure 8A, the respective voltage-controlled memristor SDR, depicted in black in Figure 9A, and obtained by plotting the state evolution function of Equation (5) with  $v_m = V_s$  against the state x, admits a triplet of intersections with the horizontal axis, namely  $X_l = 301$ , X = 478, and  $X_r =$ 1,601, of which the intermediate one is unstable. Let us now insert a series resistance of value  $R_s = 10.59 \,\Omega$  between a DC voltage source of value  $V_s = 1 \text{ V}$  and the memristor. Also in this second scenario the memristor exhibits three possible equilibria, specifically  $X_l = 319$ , X = 478, and  $X_r = 613$ , of which the center one is still unstable, as revealed by the positive slope featured therein by the resulting voltage-controlled memristor SDR, drawn in red in **Figure 9A**, and derived by expressing the memristor voltage  $v_m$ —refer to the circuit in **Figure 8A**—as

$$v_m(x) = \frac{1}{1 + R_s \cdot G(x)} \cdot V_s. \tag{11}$$

Finally, let us now increase the resistance  $R_s$  of the series resistance up to 330  $\Omega$ , and set the value  $V_s$  of the DC voltage source to 2.9 V. The SDR, which the voltage-driven threshold switch features in this scenario, is illustrated in blue in **Figure 9A**. Remarkably, the locus of the time derivative of the state vs. the state itself in this occasion crosses the horizontal axis only once in the location X = 478 with a negative slope. Thus, in this third scenario, the parameter setting of the biasing circuit of Figure 8A permits the stabilization of the NDR operating point  $Q_m$  under focus. A deeper insight into the stabilization action of the biasing circuit may be gained via its circuit-theoretic analysis. With reference to Figure 9, as shown in plot (B), the load line associated to the first scenario, where  $(V_s, R_s)$  =  $(0.937 \text{ V}, 0 \Omega)$ , is the black-colored vertical straight line  $V_m =$  $V_s = 0.937$  V, which crosses the memristor DC characteristic in a triplet of points, specifically  $Q_{m,l} = (0.937 \text{ V}, 909 \,\mu\text{A}), Q_m =$ (0.937 V, 5.948 mA), and  $Q_{m,r} = (0.937 \text{ V}, 329 \text{mA})$ , of which the intermediate one is associated with the unstable state equilibrium X = 478, as results from the analysis of the black-colored voltagecontrolled memristor SDR in plot (A). The load line associated to the biasing circuit shown in Figure 8A for  $R_s \neq 0 \Omega$  is mathematically described by 19

$$I_m = \frac{V_s - V_m}{R_s}. (12)$$

For  $(V_s, R_s) = (1 \text{ V}, 10.59 \Omega)$ , referring to the second scenario, the load line, depicted in red in **Figure 9B**, also crosses the device DC  $I_m$ – $V_m$  locus in three points, namely  $Q_{m,l} = (0.986 \text{ V}, 1.294 \text{ mA})$ ,  $Q_m = (0.937 \text{ V}, 5.948 \text{ mA})$ , and  $Q_{m,r} = (0.875 \text{ V}, 11.82 \text{ mA})$ , of which the center one is associated to the unstable state equilibrium X = 478, as follows from the investigation of the red-colored voltage-controlled memristor SDR in **Figure 9A**. With reference to **Figure 9**, in the third scenario, where  $(V_s, R_s) = (2.9 \text{ V}, 330 \Omega)$ , the load line, depicted in blue in plot (B), crosses the device DC  $I_m$ – $V_m$  locus in a single point, specifically the desired one, i.e.,  $Q_m = (0.937 \text{ V}, 5.948 \text{ mA})$ , which is associated to the globally asymptotically stable state equilibrium X = 478, as results from the study of the blue-colored voltage-controlled memristor SDR in plot (A).

REMARK 4. With reference to **Figure 9**, plot (C) offers a close-up view of plot (B) in the region surrounding the desired bias point

<sup>&</sup>lt;sup>18</sup>Note that a unique memristor state X is associated to each point  $Q_m = (V_m, I_m)$  along the DC  $I_m - V_m$  characteristic, as clear from **Figure 2**.

<sup>&</sup>lt;sup>19</sup>Inspecting the mathematical formula (11) for the voltage  $v_m$  falling across the memristor in the circuit shown in **Figure 8A** for  $R_s \neq 0 \Omega$ , it is clear that the DC value  $V_s$  of the voltage source, which allows the load line, described by Equation (12), to cross the device DC current-voltage locus in the desired NDR operating point  $Q_m$  depends upon the choice of the resistance  $R_s$ .

FIGURE 5 | Load line method for the identification of all the possible operating points of the device under any DC voltage (current) input  $V_m$  ( $I_m$ ) from the set  $S_{V_m} = \{0, 0.625, 0.875, 1.04\} \lor (S_{l_m} = \{0, 0.31, 0.68, 11.80, 207, 492\} mA)$ . (A) Unique operating point  $Q_m = (0 \lor 0, 0 mA) (Q_m = (0.625 \lor 0.031 mA))$ , marked via a magenta (blue) filled circle, which the black-colored DC  $I_m$ - $V_m$  locus identifies either with the magenta (blue) vertical load line, resulting from the application of a DC voltage  $V_s$  of value 0 (0.625) V directly across the memristor, or, alternatively, with the magenta (blue) horizontal load line, associated to the insertion of a current  $I_s$  of value 0 (0.31) mA into the NbO device. As expected from the magenta (blue) SDR, corresponding to the respective DC voltage or current value, and shown in Figures 4A,B, respectively, the first (latter) operating point is globally asymptotically stable. (B) Triplet of operating points, namely  $Q_{m,l} = (0.875 \, \text{V}, 0.68 \, \text{mA})$ ,  $Q_m = (0.875 \text{ V}, 11.80 \text{ mA})$ , and  $Q_{m,r} = (0.875 \text{ V}, 207 \text{ mA})$ , denoting the intersections of the black-colored DC  $I_m - V_m$  locus with the red vertical load line, resulting from the application of a DC voltage of value 0.875 V directly across the memristor. As inferrable from the red SDR in Figure 4A, the lower and upper operating points, marked via red filled circles (the middle operating point, marked via a red hollow circle), are locally stable (is unstable) under voltage control.  $Q_{m,l}$ ,  $Q_m$ , and  $Q_{m,r}$  may also be independently set by driving the NbO memristor with a DC current of value 0.68, 11.80, and 207 mA, respectively, as identified by the intersection of the device DC characteristic with the red horizontal load line in solid, dashed, and dash-dotted line style, respectively. As may be evinced by the red solid, dashed, and dashed-dotted SDRs in Figure 4B, the lower, middle, and upper operating point in this triplet is globally asymptotically stable under current control [even Q<sub>m</sub> is thus marked via a red filled circle in (B)). (C) Unique operating point  $Q_m = (1.04 \text{ V}, 492 \text{ mA})$ , marked via a brown filled circle, which the black-colored DC  $I_m - V_m$  locus identifies either with the brown vertical load line, resulting from the application of a DC voltage V<sub>s</sub> of value 1.04 V directly across the memristor, or with the brown horizontal load line, associated to the insertion of a current Is of value 492 mA into the NbO device. As expected from the brown SDR, corresponding to the respective DC voltage or current value, and shown in Figures 4A,B, respectively, this operating point is globally asymptotically stable, irrespective of the nature of the device control signal.

$Q_m=(0.937\,\mathrm{V},\,5.948\,\mathrm{mA})$  on the NDR region of the device DC characteristic. It is instructive to pinpoint that, unless what emerges in the first and second scenarios, for  $(V_s,R_s)=(2.9\,\mathrm{V},330\,\Omega)$  the modulus of the negative slope of the load line at  $Q_m$  is smaller than the modulus of the negative slope of the memristor DC  $I_m$ - $V_m$  locus at the same point, i.e.,

$$\frac{1}{R_s} = 3.03 \text{ mS} < -\frac{dv_m}{di_m} \bigg|_{Q_m = (0.937 \text{ V}, 5.948 \text{mA})} = 60.555 \text{ mS}.$$

In fact, the stabilization of a DC operating point  $Q_m$  along the NDR region of the memristor DC locus is guaranteed as long as

$$R_{s} > -r \mid_{O_{m}}, \tag{13}$$

where, as anticipated in section 2.2,  $r|_{Q_m}$ , the small-signal or differential or local resistance at  $Q_m$ , is defined as

$$r \mid_{Q_m} \triangleq \left( \frac{dv_m}{di_m} \mid_{Q_m} \right)^{-1} .$$

(14)

**FIGURE 6** | Response of the NbO threshold switch to the application of an independent source of DC voltage  $V_s$  between its two terminals. **(A)** Memristor current (blue) under DC voltage stress with  $V_s = 0.625 \,\mathrm{V}$  (red). Here, the load line—refer to the vertical blue line in **Figure 5A**—intersects the memristor DC locus in the lower PDR branch. **(B)** Time waveform of the memristor state, converging to the globally asymptotically stable value X = 267 as t tends to  $\infty$ . **(C)** Dash-dotted (solid) blue waveform: Current through the NbO micro-structure under DC voltage stress with  $V_s = 0.875 \,\mathrm{V}$  (red) and for an initial condition  $x_0$  smaller (larger) than the unstable memristor operating state X = 612, constituting the separatrix between the basins of attraction of the two-locally stable bias memory states  $X_f = 289$  and  $X_f = 1456$  (recall **Figure 4**). Here the load line—refer to the vertical red line in **Figure 5B**—crosses the memristor DC characteristic in the NDR region, where the unstable operating point lies, as well as in either of the two PDR regions, where the threshold switch may be found asymptotically. **(D)** Dash-dotted (solid) blue solution: Time evolution of the memristor state, converging to the locally asymptotically stable value  $X_f = 289 \,(X_f = 1,456)$  as t tends to  $\infty$ , for  $x_0 < (>)X = 612$ .

**FIGURE 7** Model numerical simulation demonstrating the inherently stable nature of the NDR operating point  $Q_m = (V_m, I_m) = (0.875 \text{ V}, 11.80 \text{ mA})$  under current control. A DC source of current  $I_s = 11.80 \text{ mA}$ , shown through the red color in **(A)**, is applied directly across the NbO threshold switch. The resulting time waveforms of memristor voltage [in blue in **(A)**] and state [in blue in **(B)**] approach asymptotically the DC values  $V_m = 0.875 \text{ V}$ , and X = 612, respectively. The initial condition  $X_0$  was arbitrarily chosen as 253.15.

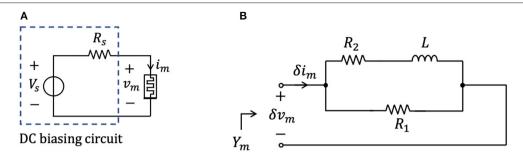

**FIGURE 8** | **(A)** Biasing circuit for the stabilization of a given NDR operating point  $Q_m = (V_m, I_m)$  on the threshold switch DC current-voltage characteristic. The introduction of a linear resistor of suitable resistance  $R_s$  between the DC voltage source  $V_s$  and the threshold switch is instrumental in stabilizing the NDR operating point. As will be clarified shortly, the condition for stabilizing  $Q_m$  is  $R_s > -r \mid_{Q_m}$ , where  $r \mid_{Q_m}$  denotes the device small-signal resistance at the operating point under focus. **(B)** Small-signal equivalent circuit model of the voltage-controlled NbO memristor. The small-signal input admittance  $Y_m(s)$  of the first-order memristive cell is computed from the port across the device.

Choosing the resistance of the series resistor such that

$$R_{\rm s} > \hat{r},$$

(15)

with

$$\hat{r} \triangleq \max_{\forall Q_m : r \mid_{Q_m} < 0 \Omega} \{ -r \mid_{Q_m} \}$$

(16)

denoting the largest modulus of the differential resistance across the NDR region of the device DC characteristic is sufficient to stabilize every operating point along it. With reference to **Figure 3**, for our NbO threshold switch  $\hat{r}=21.43~\Omega$  at X=411, and the series resistor resistance adopted most frequently in this article, i.e.,  $R_s=330~\Omega$ , is large enough to stabilize the entire NDR region of its DC  $I_m$ - $V_m$  locus.

**Figure 10** demonstrates that, setting the biasing circuit parameters  $V_s$  and  $R_s$  in the circuit of **Figure 8A** to 2.9 V, and 330  $\Omega$ , respectively, the memristor state, voltage, and current settle asymptotically to the desired values X=478,  $V_m=0.937$  V, and 5.948 mA, respectively.

### 3. LA AND EOC IN THE NBO VOLATILE MEMRISTOR

Before gaining a deep insight into the conditions under which the NbO threshold switch may enter the LA domain, and, most importantly, its "pearl"-subdomain, i.e., the EOC, let us define rigorously the fundamental concepts of LA and EOC.

#### 3.1. LA and EOC: A Rigorous Definition

Without loss of generality, a first-order voltage-controlled<sup>20</sup> twoterminal memristor device with dynamic state x is considered here for introducing this fundamental notion. Let an opportune biasing circuit polarize the memristor in a certain point  $Q_m=(V_m,I_m)$  of its DC current  $I_m$ -voltage  $V_m$  characteristic. Assume that an infinitesimal voltage signal  $\delta v_m$  is superimposed on the memristor bias voltage  $V_m$  at  $t=t_0$ , generating a total voltage over the device equal to  $v_m=V_m+\delta v_m$  thereafter. As a result, the device bias state X and current  $I_m$  also drift by infinitesimal quantities, namely  $\delta x$  and  $\delta i_m$ , respectively, leading to an overall state expressed by  $x=X+\delta x$ , and to a total current in the form  $i_m=I_m+\delta i_m$  from the time instant of application of the local perturbation. The memristor is said to be *locally active* at  $Q_m$  if and only if it is possible to identify at least one infinitesimal perturbation  $\delta v_m=\delta v_m^*$  such that the small-signal or local net energy  $\delta \mathcal{E}(t_0;t)$  absorbed by the device over the time interval  $[t_0,t]$ , and computed via

$$\delta \mathcal{E}(t_0; t) = \int_{t'=t_0}^{t'=t} \delta \nu_m(t') \cdot \delta i_m(t') dt', \tag{17}$$

by assuming the associated reference direction convention for memristor voltage and current<sup>21</sup> (Chua, 1987), is found to be negative for at least one finite time instant  $t=t^*$ . This rigorous definition is however impractical for testing whether a memristor may ever enter the locally active regime, where it may amplify infinitesimal fluctuations in energy. In fact, before concluding that the device is LP across its entire DC current-voltage characteristic, one should ensure that the integral (17) keeps positive at all times and for each of the infinitely many infinitesimal perturbations, which may ever stimulate the memristor, and iterate this procedure for each of the infinitely many one-port bias points. However, and fortunately, there exists a theorem, known as LA Theorem (Chua, 2005), which provides necessary and sufficient conditions under which a one-port is locally active at a given operating point  $Q_m$ . The theorem

<sup>&</sup>lt;sup>20</sup>Invoking the duality principle (Chua, 1987), similar conclusions apply mutatis mutandis to a first-order current-controlled two-terminal memristor. Furthermore, the local activity definition may be extended also to higher-order one- and multi-ports of memristive or non-memristive nature, as explained in Chua (1998).

<sup>&</sup>lt;sup>21</sup> According to this convention, once a reference direction is chosen for the voltage falling across a two-terminal electrical circuit element, the current is assumed to flow into the one-port from the terminal, which is assigned a positive polarity (Chua, 1987).

**FIGURE 9 | (A)** Black curve: State Dynamic Route (SDR) of the memristor under the application of a DC voltage  $V_s = 0.937$  V directly across it. Under these circumstances, the NbO device is bistable, with the basins of attraction of the left locally stable state operating point  $X_l$ , lying at 301, and of the right locally stable state operating point  $X_l$ , lying at 1,601, separated by an intermediate unstable state operating point,  $X_l$ , lying at 478. Importantly, the memristor voltage  $V_m$  and current  $I_m$ , corresponding to the state operating point X = 478, and identifying the coordinates of a NDR point  $Q_m$  on the device current-voltage locus, are 0.937 V and 5.948 mA, respectively. Red curve: Memristor SDR under the application of a DC voltage  $V_s = 1$  V in the circuit of **Figure 8A** with  $R_s = 10.59$  Ω. Under these circumstances, the biasing circuit is unable to stabilize the state operating point X = 478, which, similarly as in the previous case, separates the basins of attractions of two locally stable state operating points, i.e.,  $X_l = 319$  and  $X_r = 613$ , located on its left and right, respectively. Blue curve: SDR of the memristor under the application of a DC voltage  $V_s = 2.9$  V across the series between a linear resistor of resistance  $R_s = 330$  Ω and the memristor itself. In this scenario, the memristor features a single globally asymptotically stable state operating point, lying at the desired location X = 478. **(B)** DC current voltage-characteristic of the NbO device (green curve), load line corresponding to the scenario where a DC voltage source of value  $V_s = 0.937$  V is applied directly across the threshold switch (black vertical segment), load line in the case where a DC voltage source of value  $V_s = 1$  V is applied across the series combination between the memristor and a linear resistor with resistance  $R_s = 10.59$  Ω (red negative-sloped segment), and load line for the circuit shown in **Figure 8A** with  $V_s = 2.9$  V and  $R_s = 330$  Ω (blue negative-sloped segment)

statement, here adapted to a first-order voltage-controlled<sup>22</sup> two-terminal memristor device, is enunciated below.

REMARK 5. Under voltage control a first-order memristive oneport is said to be locally active at a certain operating point  $Q_m = (V_m, I_m)$  if and only if its local input admittance about  $Q_m$  satisfies at least one of 4 conditions. Defining the local transfer function of the voltage-controlled one-port about  $Q_m$  as  $H_m(s) \triangleq Y_m(s)$ , where  $Y_m(s) = \frac{\mathcal{L}\{\delta i_m(t)\}}{\mathcal{L}\{\delta v_m(t)\}}$  denotes the device small-signal admittance, the 4 conditions<sup>23</sup> may be expressed as follows<sup>24</sup>:

- 1.  $Y_m(s)$  has a single pole  $s = s_{p,Y_m}$  on the right half of the complex plane (RHP), i.e.,  $\Re\{s_{p,Y_m}\} > 0$ .

- 2.  $Y_m(s)$  has a single pole  $s = s_{p,Y_m} = j\omega_{p,Y_m}$  lying on the imaginary axis, i.e.,  $\Re\{s_{p,Y_m}\} = 0$ , and featuring an either complex-valued or negative real-valued residue<sup>25</sup>.

$<sup>^{22} \</sup>rm Invoking$  the duality principle (Chua, 1987), similar conclusions apply mutatis mutandis to a first-order current-controlled two-terminal memristor. Furthermore, the LA theorem may be generalized for the analysis of higher-order one- and multi-ports of memristive or non-memristive nature, as described in Chua (1998).

<sup>&</sup>lt;sup>23</sup>For a first-order current-controlled memristive one-port, the local transfer function about  $Q_m$  is defined as  $H_m(s) \triangleq Z_m(s)$ , where  $Z_m(s) \triangleq \frac{\mathcal{L}(\delta \nu_m(t))}{\mathcal{L}(\delta l_m(t))}$  represents the device small-signal impedance.

<sup>&</sup>lt;sup>24</sup>With reference to the 4th condition,  $Y_m^*(j\omega)$  denotes the complex conjugate of  $Y_m(j\omega)$ .

<sup>&</sup>lt;sup>25</sup>The residue of a *mth*-order pole  $s = s_{p,Y_m}$  of the device local admittance  $Y_m(s)$  may be calculated via  $k_{s_{p,Y_m}} = \frac{1}{(m-1)!} \cdot \lim_{s \to s_{p,Y_m}} \frac{d^{m-1}}{ds^{m-1}} \left( (s - s_{p,Y_m})^m \cdot Y_m(s) \right)$ .

**FIGURE 10** Proof of evidence for the stabilization of the NDR operating point  $Q_m = (V_m, I_m) = (0.937 \text{ V}, 5.948 \text{ mA})$  under voltage control on the basis of a numerical simulation of the polynomial-based model. With reference to the circuit of **Figure 8A**, a resistor of resistance  $R_s = 330 \Omega$  is inserted between the source, generating a DC voltage  $V_s$  of value 2.9 V [see **(A)**], and the memristor. As shown in **(B-D)**, the memristor state, voltage, and current in turn converge toward the DC values X = 478,  $V_m = 0.937 \text{ V}$ , and  $I_m = 5.948 \text{ mA}$  as time goes to infinity. The DAE set initial condition  $x_0$ , which may be chosen arbitrarily here, was fixed to 253.15.

- 3.  $Y_m(s)$  has a pole  $s = s_{p,Y_m} = j\omega_{p,Y_m}$  of order m > 1 and located on the imaginary axis<sup>26</sup>.

- 4.  $Y_m(j\omega) + Y_m^*(j\omega) < 0$  for at least one non-negative real-valued angular frequency  $\omega = \omega_{0,Y_m}$ .

If and only if one and only one of the four conditions in this list, particularly the last one, holds true, the one-port is locally active around an asymptotically stable operating point  $Q_m$ . In this case, the locally active one-port is said to be on the EOC, which has been dubbed the "pearl" of the LA domain in Chua (2005). If none of the four conditions listed above applies, the one-port is said to be LP at the given operating point.

### 3.2. Small-Signal Equivalent Circuit Model of the NbO Memristor

This section intends to derive the small-signal equivalent circuit model of the voltage-controlled threshold switch to allow the determination of its local admittance function  $Y_m(s)$ . Let us indicate with X the state operating point of the memristor under a DC voltage stimulus  $V_m$  falling between its terminals, and with  $I_m$  the resulting current flowing through the circuit element. With  $\delta x \triangleq x - X$  denoting an infinitesimal change in the memristor state x with respect to its operating point X, resulting from the application of a small-signal perturbation  $\delta v_m$  in addition to the DC bias voltage  $V_m$  across its terminals, the linearization of state equation (3) and Ohm's law (4), with state evolution and memductance functions expressed by Equations (5) and (6),

respectively, provides the following small-signal or local model for the NbO-based memristor:

$$\frac{d\delta x}{dt} = a \cdot \delta x + b \cdot \delta v_m \tag{18}$$

$$\delta i_m = c \cdot \delta x + d \cdot \delta v_m \tag{19}$$

where  $\delta i_m$  stands for a local variation in the memristor current with respect to the DC current  $I_m$  due to the small-signal voltage input  $\delta v_m$ , while the formulas for the local memristor model coefficients a, b, c, and d, respectively, are

$$a = \frac{\partial \dot{x}(x, v_m)}{\partial x} \Big|_{(x, v_m) = (X, V_m)}$$

$$= a_1 + (c_{21} + 2 \cdot c_{22} \cdot X + 3 \cdot c_{23} \cdot X^2 + 4 \cdot c_{24} \cdot X^3 + 5 \cdot c_{25} \cdot X^4) \cdot V_m^2,$$

$$(20)$$

$$b = \frac{\partial \dot{x}(x, v_m)}{\partial v_m} \Big|_{(x, v_m) = (X, V_m)}$$

$$= 2 \cdot (b_2 + c_{21} \cdot X + c_{22} \cdot X^2 + c_{23} \cdot X^3 + c_{24} \cdot X^4 + c_{25} \cdot X^5) \cdot V_m,$$

$$c = \frac{\partial i_m(x, v_m)}{\partial x} \Big|_{(x, v_m) = (X, V_m)}$$

$$= (d_1 + 2 \cdot d_2 \cdot X + 3 \cdot d_3 \cdot X^2 + d_4 \cdot d_4 \cdot X^3) \cdot V_m, \text{ and}$$

$$d = \frac{\partial i_m(x, v_m)}{\partial v_m} \Big|_{(x, v_m) = (X, V_m)}$$

$$(22)$$

$= G(X) = d_0 + d_1 \cdot X + d_2 \cdot X^2 + d_3 \cdot X^3 + d_4 \cdot X^4.$  (23)

$<sup>^{26}</sup>$ The 3rd condition may never hold true for a first-order one-port.

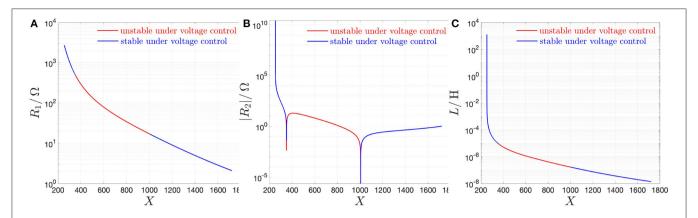

**FIGURE 11** | Loci of the resistance  $R_1$  (**A**), of the modulus of the resistance  $R_2$  (**B**), and of the inductance L (**C**) in the small-signal equivalent circuit model of the NbO threshold switch from NaMLab as a function of the memristor state operating point X. In each plot, the red (blue) color is assigned to each branch corresponding to unstable (stable) state operating points under voltage control. As expected, given that it represents the instantaneous resistance  $R = G^{-1}$  of the threshold switch, which is a passive device,  $R_1$  is positive at all operating points.  $R_2$  is found to have a negative sign throughout the red-colored branch, i.e., along the whole NDR region of the memristor DC  $I_m - V_m$  characteristic (note, however, that  $R_1 + R_2$  is found to be positive at all operating points). Finally, the sign of L is positive irrespective of X.

**FIGURE 12** | Pole-zero diagram for the local admittance of the voltage-controlled NbO threshold switch from NaMLab GgmbH. While the zero is negative throughout the state operating domain  $X \in [X_a, X_b] = [253, 1,722]$  from **Figure 2**, the pole is negative (positive) in either of the two PDR regions  $X \in [X_a, X_1) = [253, 351)$  and  $X \in (X_2, X_b] = (1,006, 1,722]$  [throughout the NDR region  $X \in (X_1, X_2) = (351, 1,006)$ ] of the threshold switch DC characteristic. Here  $s_{\mathcal{P}_1, Y_m}$  ( $s_{\mathcal{Z}_1, Y_m}$ ) and  $s_{\mathcal{P}_2, Y_m}$  ( $s_{\mathcal{Z}_2, Y_m}$ ), respectively, are the values of the pole (zero) of  $Y_m(s)$  at the lower  $X_1$  and upper  $X_2$  bounds of the NDR state bias domain.

Taking the Laplace transform of each side in the local form of the state equation (18), with x(0) = 0, as well as of Ohm's law (19), we obtain:

$$s \cdot \mathcal{L}\{x(t)\} = a \cdot \mathcal{L}\{x(t)\} + b \cdot \mathcal{L}\{v_m(t)\}$$

(24)

$$\mathcal{L}\{i_m(t)\} = c \cdot \mathcal{L}\{x(t)\} + d \cdot \mathcal{L}\{v_m(t)\}. \tag{25}$$

Solving Equation (24) for  $\mathcal{L}\{x(t)\}$ , and inserting the resulting expression into Equation (25), the admittance-based transfer function  $Y_m(s)$ , defining, within the s-domain, the current response of the micro-scale device to a small-signal voltage

stimulation around the operating point, is found to be expressed by

$$Y_m(s) = \frac{\mathcal{L}\{i_m(t)\}}{\mathcal{L}\{v_m(t)\}} = d \cdot \frac{s - \frac{a \cdot d - b \cdot c}{d}}{s - a}.$$

(26)

$Y_m(s)$  represents the memristor small-signal or local or infinitesimal admittance. Its formula in Equation (26) may be implemented in circuit-theoretic form via the circuit, shown in **Figure 8B**, and consisting of the parallel combination between a linear resistor  $R_1$ , and the series connection between yet another linear resistor  $R_2$  and a linear inductor L. Of course, the values of the parameters of the electrical elements in this figure, showing essentially the small-signal equivalent circuit model of the NbO memristor, depend upon the memristor operating point under focus. From basic circuit-theoretic principles, the Laplace domain representation of the admittance of the one-port in **Figure 8B** is found to be expressed by

$$Y_m(s) = \frac{1}{R_1} \cdot \frac{s + \frac{R_1 + R_2}{L}}{s + \frac{R_2}{L}}.$$

(27)

Imposing the equivalence between the formula (27) for Y and the analytical expression (26) for  $Y_m$  establishes the following constraints on the dependence of the parameters of the circuit of **Figure 8B** on the memristor bias point<sup>27</sup>:

$$R_1 = \frac{1}{d},\tag{28}$$

$$R_2 = -\frac{a}{b \cdot c}, \quad \text{and} \tag{29}$$

$$L = \frac{1}{b \cdot c}. (30)$$

$<sup>^{27}</sup>$ Unless otherwise stated, in the remainder of the paper the memristor small-signal admittance  $Y_m$  will be expressed in terms of the parameters of the device small-signal equivalent circuit model of **Figure 8B**, i.e., through Equation (27).

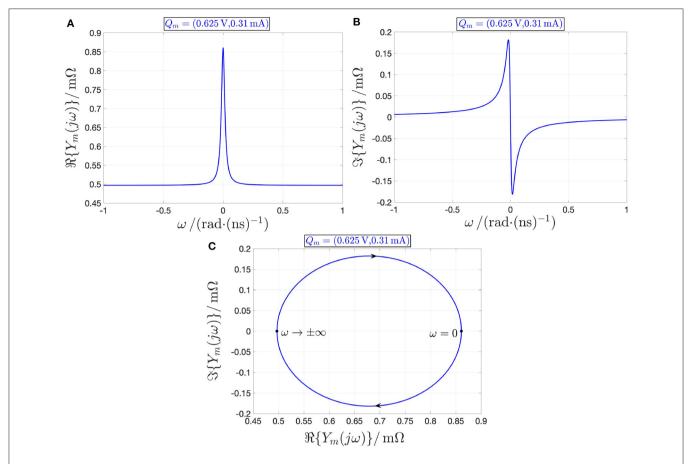

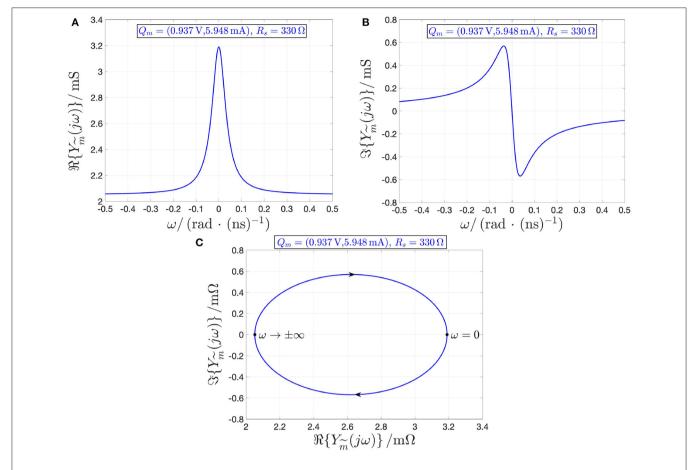

**FIGURE 13** Loci of the real **(A)** and imaginary **(B)** parts of the local impedance  $Y_m(j\omega)$  of the memristor vs. the angular frequency  $\omega$  at the operating point  $Q_m = (V_m, I_m) = (0.625 \, \text{V}, 0.31 \, \text{mA})$ . **(C)** Locus of  $\Im\{Y_m(j\omega)\}$  vs.  $\Re\{Y_m(j\omega)\}$ , as computed from **(A,B)**, with arrows showing how the trajectory point evolves along the Nyquist plot as  $\omega$  increases from  $-\infty$  to  $+\infty$ . The real part of the device local admittance is positive for all angular frequencies. Under voltage control, the threshold switching device is locally passive at the PDR operating point  $Q_m$  under focus.

**Figures 11A–C** illustrate the resistance  $R_1$ , the modulus of the resistance  $R_2$ , and the inductance L as a function of the memristor state operating point X, respectively. In each plot, the state operating points along the red (blue) branches are unstable (stable) under voltage control, as discussed in section 2.2. Importantly, the resistance  $R_2$  is negative throughout the red branch, i.e., for all X-values in the range [351, 1, 006], which corresponds to the entire NDR region of the memristor DC current-voltage characteristic of **Figure 2C**.

Inserting the expression for d from Equation (23) into the formula (28) for  $R_1$ , the device instantaneous resistance<sup>28</sup>  $R \equiv G^{-1}$  may be simply obtained via the resistance of the purely resistive branch in the circuit of **Figure 8B**, i.e.,

$$R = R_1. (31)$$

Additionally, the small-signal resistance r of the threshold switch may be computed as the parallel combination of the

two resistances in the small-signal equivalent circuit model of **Figure 8B**, i.e.,

$$r = R_1 || R_2. (32)$$

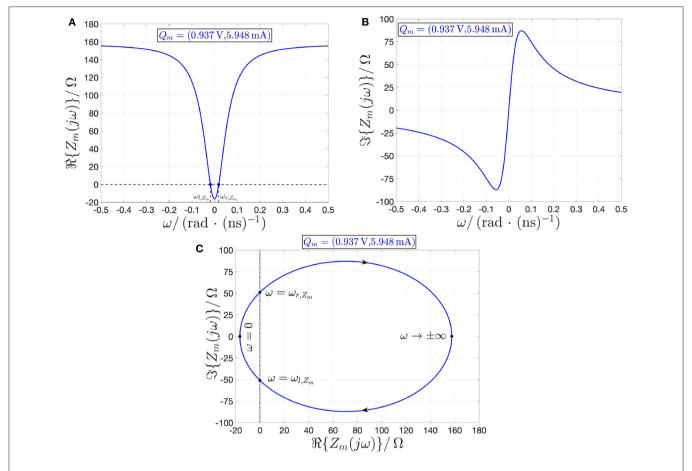

$Y_m(s)$  admits a zero  $s_{z,Y_m}$  and a pole  $s_{p,Y_m}$ , respectively, located at

$$s_{z,Y_m} = -\frac{R_1 + R_2}{L}$$

, and at (33)

$$s_{p,Y_m} = -\frac{R_2}{I}. ag{34}$$

**Figure 12** illustrates the pole-zero diagram of the local admittance  $Y_m(s)$  of the NbO volatile memristor from NaMLab using a blue (red) color in either of the PDR regions (in the NDR region). While the zero from Equation (33), shown through a dash-dotted line, is negative for all the memristor state bias points within the set  $X \in [X_a, X_b] = [253, 1,722]$ , the pole, located as specified in Equation (34), and depicted by means of a solid line, assumes positive values across the NDR region, i.e.,

<sup>&</sup>lt;sup>28</sup>By device instantaneous resistance we intend here its memristance.

for  $X \in (X_1, X_2) = (351, 1, 006)$ , holding the opposite sign in the lower PDR region, i.e., for  $X \in [X_a, X_1) = [253, 351)$ , and in the upper PDR region, i.e., for  $X \in (X_2, X_b] = (1, 006, 1, 722]$ .

REMARK 6. The analyses in sections 2.2 and 2.3 have revealed that, without the series resistor, i.e., for  $R_s = 0 \Omega$  in the circuit of **Figure 8A**, any bias point  $Q_m = (V_m, I_m)$  lying on the NDR region of the memristor DC current-voltage characteristic is unstable under voltage control. This may be inferred also by observing that the pole  $s_{p,Y_m}$  of the device local admittance sits on the RHP for each bias point of this kind. Moreover, it is instructive to note that the pole  $s_{p,Y_m}$  of the device local admittance  $Y_m$  coincides with the eigenvalue  $\lambda$  of the linearized form of the memristor state

in **Figure 8A** is chosen so as to meet the constraint (13), where  $r|_{Q_m}$  is the threshold switch small-signal resistance r, expressed in (32) as a function of the parameters  $R_1$  and  $R_2$  of the small-signal equivalent circuit shown in **Figure 8B**, and evaluated at the associated operating point  $Q_m = (V_m, I_m)$ . It is worth to point out that the pole  $s_{p,Y_m}$  of the combined device local admittance  $Y_m$  about  $Q_m$  coincides with the eigenvalue  $\tilde{\lambda}$  of the linearized form of the memristor state Equation (3), with state evolution function expressed by Equation (5), around the corresponding threshold switch state operating point X, i.e., recalling that, for  $R_s \neq 0 \Omega$  in the circuit shown in **Figure 8A**, the voltage across the memristor is a function  $v_m = v_m(x)$  of the memory state x as dictated by the voltage divider formula (11),

$$\tilde{\lambda} = \frac{d\dot{x}}{dx}\Big|_{x=X} = a_1 + (c_{21} + 2 \cdot c_{22} \cdot X + 3 \cdot c_{23} \cdot X^2 + 4 \cdot c_{24} \cdot X^3 + 5 \cdot c_{25} \cdot X^4) \cdot v_m^2(X) - 2 \cdot R_s \cdot v_m^2(X)$$

$$\cdot \frac{(b_2 + c_{21} \cdot X + c_{22} \cdot X^2 + c_{23} \cdot X^3 + c_{24} \cdot X^4 + c_{25} \cdot X^5) \cdot (d_1 + 2 \cdot d_2 \cdot X + 3 \cdot d_3 \cdot X^2 + 4 \cdot d_4 \cdot X^3)}{1 + R_s \cdot (d_0 + d_1 \cdot X + d_2 \cdot X^2 + d_3 \cdot X^3 + d_4 \cdot X^4)}$$

$$\equiv s_{p,Y_{\tilde{m}}}, \qquad (38)$$

Equation (3), with state evolution function expressed by Equation (5), around the same operating point, i.e., recalling that, for  $R_s = 0 \Omega$  in the circuit of **Figure 8A**, the voltage  $V_m$  across the memristor is just a constant, as established by the DC source,

$$\lambda = \frac{d\dot{x}}{dx}\Big|_{x=X} = a_1 + c_{21} \cdot V_m^2 + 2 \cdot c_{22} \cdot V_m^2 \cdot X$$

$$+3 \cdot c_{23} \cdot V_m^2 \cdot X^2 + 4 \cdot c_{24} \cdot V_m^2 \cdot X^3 + 5 \cdot c_{25} \cdot V_m^2 \cdot X^4$$

$$\equiv s_{p,Y_m}, \tag{35}$$

where the latter equivalence descends from Equations (20), (29), (30), and (34). It follows that the locus of the eigenvalue  $\lambda$  vs. the state operating point X coincides with the diagram of the pole (34) of the device local admittance  $Y_m(s)$ , shown via a solid line in Figure 8.

Interestingly, inspecting the formula of the local admittance  $Y_{\widetilde{m}}$  of the combined memristor, consisting of the series combination between the linear resistor  $R_s$  and the threshold switch, about the respective operating point  $Q_{\widetilde{m}} = (V_{\widetilde{m}}, I_{\widetilde{m}})$ , with  $V_{\widetilde{m}} = V_m + R_s \cdot I_m$ , and  $I_{\widetilde{m}} = I_m$ , i.e.,

$$Y_{\widetilde{m}}(s) = \frac{1}{R_1 + R_s} \cdot \frac{s + \frac{R_1 + R_2}{L}}{s + \frac{R_s \cdot (R_1 + R_2) + R_1 \cdot R_2}{L \cdot (R_1 + R_s)}},$$

(36)

it is easy to verify that, as expected from the investigation from section 2.2, its pole  $s_{p,Y_{\widetilde{m}}}$ , expressed by

$$s_{p,Y_{\widetilde{m}}} = -\frac{R_s \cdot (R_1 + R_2) + R_1 \cdot R_2}{L \cdot (R_1 + R_s)},$$

(37)

resides on the left half of the complex plane (LHP) as long as the resistance  $R_s$  of the series resistor in the biasing circuit shown

where the last equivalence descends from Equations (20), (21), (22), (23), and (37).

# 3.3. Classification of the LP, LA, and EOC Regimes of the NbO Device Under Voltage and Current Control

Under voltage control, the pole  $s_{p,Y_m}$  of the memristor local admittance  $Y_m$  about any operating point  $Q_m = (V_m, I_m)$

**TABLE 2** | Complete classification of all the possible operating regimes of the micro-scale device depending upon nature of the stimulus and location of the bias point  $Q_m = (V_m, I_m)$  on the DC characteristic.

Form of control Location of  $Q_m$  on the DC  $I_m$ - $V_m$  locus Operating regime

Voltage or current Either PDR branch

LP

Voltage (current) NDR branch

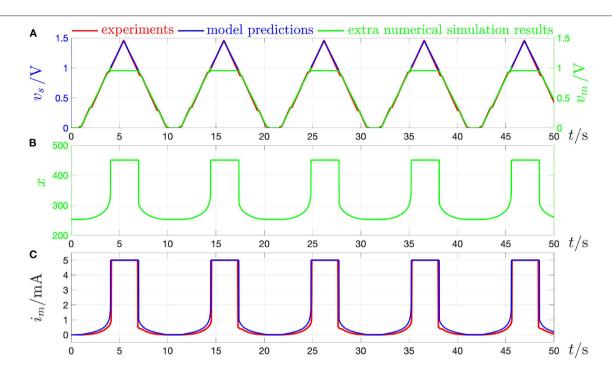

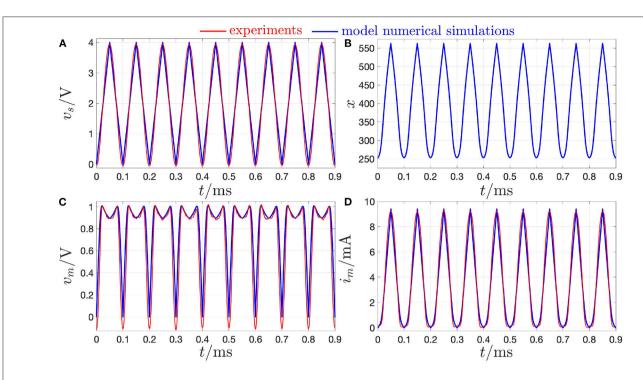

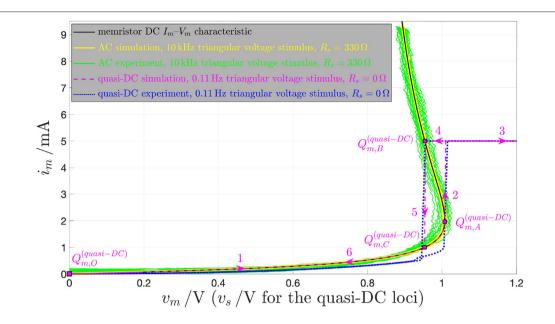

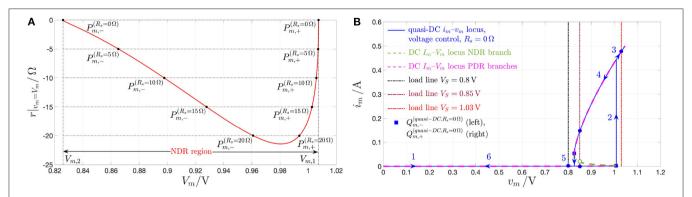

Unstable LA (EOC)