#### Frontiers eBook Copyright Statement

The copyright in the text of individual articles in this eBook is the property of their respective authors or their respective institutions or funders. The copyright in graphics and images within each article may be subject to copyright of other parties. In both cases this is subject to a license granted to Frontiers.

The compilation of articles constituting this eBook is the property of Frontiers.

Each article within this eBook, and the eBook itself, are published under the most recent version of the Creative Commons CC-BY licence. The version current at the date of publication of this eBook is CC-BY 4.0. If the CC-BY licence is updated, the licence granted by Frontiers is automatically updated to the new version.

When exercising any right under the CC-BY licence, Frontiers must be attributed as the original publisher of the article or eBook, as applicable.

Authors have the responsibility of ensuring that any graphics or other materials which are the property of others may be included in the CC-BY licence, but this should be checked before relying on the CC-BY licence to reproduce those materials. Any copyright notices relating to those materials must be complied with.

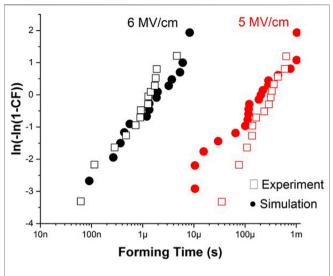

Copyright and source acknowledgement notices may not be removed and must be displayed in any copy, derivative work or partial copy which includes the elements in question.

All copyright, and all rights therein, are protected by national and international copyright laws. The above represents a summary only. For further information please read Frontiers' Conditions for Website Use and Copyright Statement, and the applicable CC-BY licence.

ISBN 978-2-88974-460-2

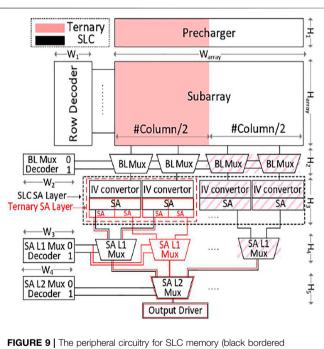

#### **About Frontiers**

Frontiers is more than just an open-access publisher of scholarly articles: it is a pioneering approach to the world of academia, radically improving the way scholarly research is managed. The grand vision of Frontiers is a world where all people have an equal opportunity to seek, share and generate knowledge. Frontiers provides immediate and permanent online open access to all its publications, but this alone is not enough to realize our grand goals.

#### **Frontiers Journal Series**

The Frontiers Journal Series is a multi-tier and interdisciplinary set of open-access, online journals, promising a paradigm shift from the current review, selection and dissemination processes in academic publishing. All Frontiers journals are driven by researchers for researchers; therefore, they constitute a service to the scholarly community. At the same time, the Frontiers Journal Series operates on a revolutionary invention, the tiered publishing system, initially addressing specific communities of scholars, and gradually climbing up to broader public understanding, thus serving the interests of the lay society, too.

#### **Dedication to Quality**

Each Frontiers article is a landmark of the highest quality, thanks to genuinely collaborative interactions between authors and review editors, who include some of the world's best academicians. Research must be certified by peers before entering a stream of knowledge that may eventually reach the public - and shape society; therefore, Frontiers only applies the most rigorous and unbiased reviews. Frontiers revolutionizes research publishing by freely delivering the most outstanding

research, evaluated with no bias from both the academic and social point of view. By applying the most advanced information technologies, Frontiers is catapulting scholarly publishing into a new generation.

#### What are Frontiers Research Topics?

Frontiers Research Topics are very popular trademarks of the Frontiers Journals Series: they are collections of at least ten articles, all centered on a particular subject. With their unique mix of varied contributions from Original Research to Review Articles, Frontiers Research Topics unify the most influential researchers, the latest key findings and historical advances in a hot research area! Find out more on how to host your own Frontiers Research Topic or contribute to one as an author by contacting the Frontiers Editorial Office: frontiersin.org/about/contact

## MEMRISTIVE NEUROMORPHICS: MATERIALS, DEVICES, CIRCUITS, ARCHITECTURES, ALGORITHMS AND THEIR CO-DESIGN

#### Topic Editors:

**Huanglong Li,** Tsinghua University, China **J. Joshua Yang,** University of Southern California, United States **Hongsik Jeong,** Ulsan National Institute of Science and Technology, South Korea

**Citation:** Li, H., Yang, J. J., Jeong, H., eds. (2022). Memristive Neuromorphics: Materials, Devices, Circuits, Architectures, Algorithms and Their Co-Design. Lausanne: Frontiers Media SA. doi: 10.3389/978-2-88974-460-2

## **Table of Contents**

## 104 Investigation on the Stabilizing Effect of Titanium in HfO<sub>2</sub>-Based Resistive Switching Devices With Tungsten Electrode

Vittorio Fra, Elmira Shahrabi, Yusuf Leblebici and Carlo Ricciardi

#### 18 Advances in Memristor-Based Neural Networks

Weilin Xu, Jingjuan Wang and Xiaobing Yan

#### 32 Reliable 2D Phase Transitions for Low-Noise and Long-Life Memory Programming

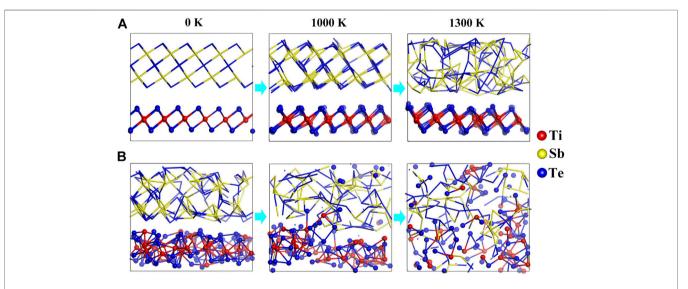

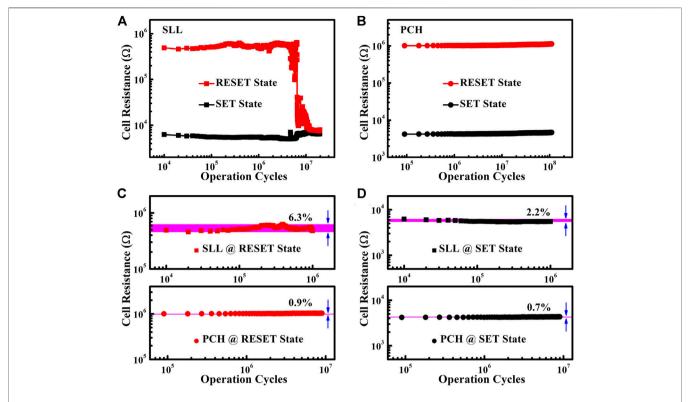

Keyuan Ding, Tianci Li, Bin Chen and Feng Rao

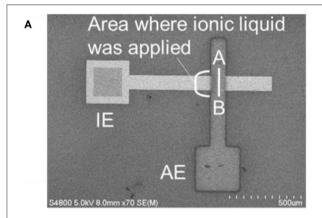

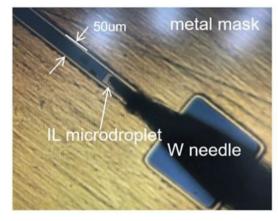

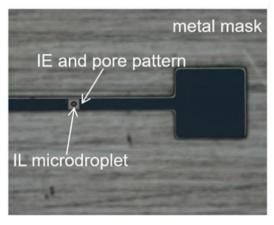

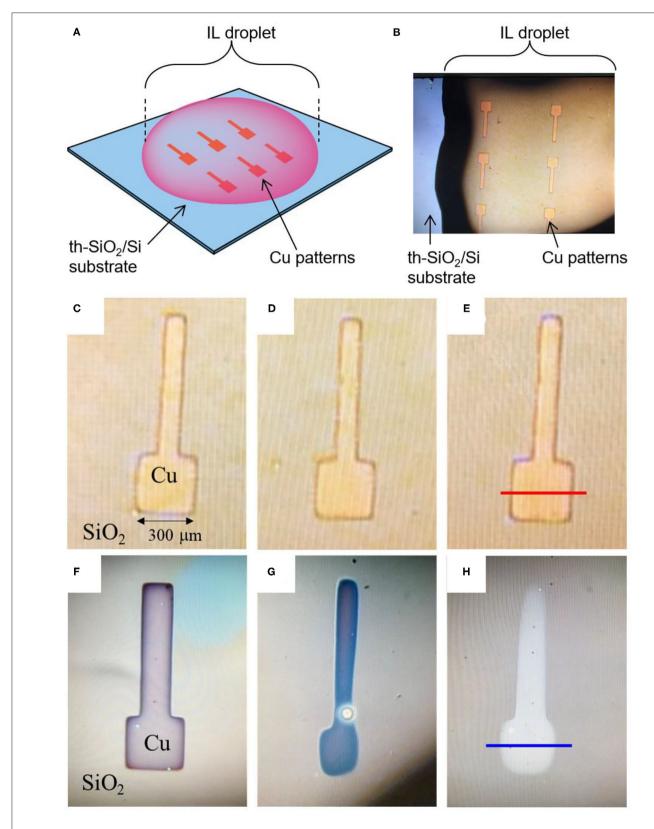

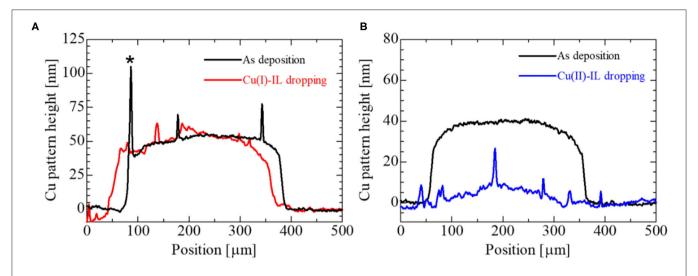

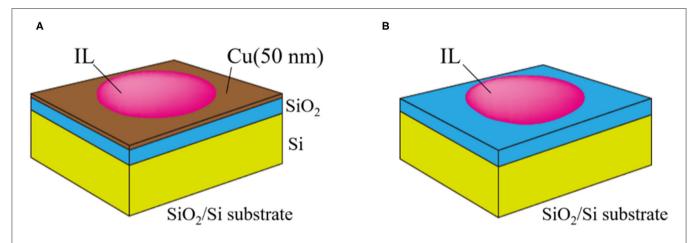

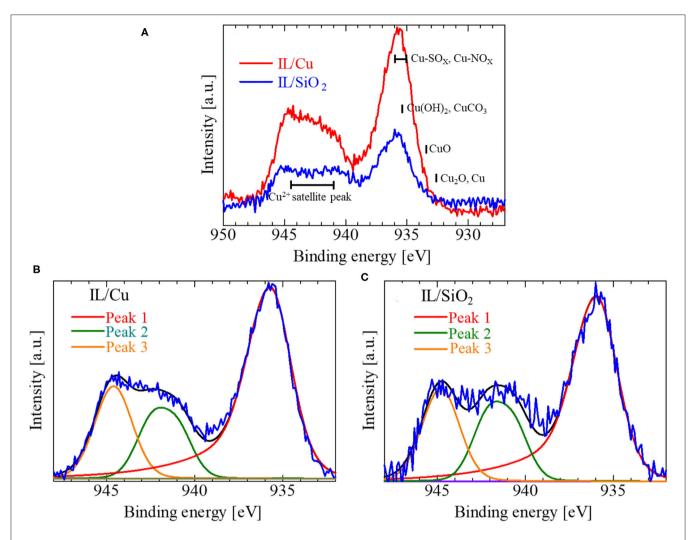

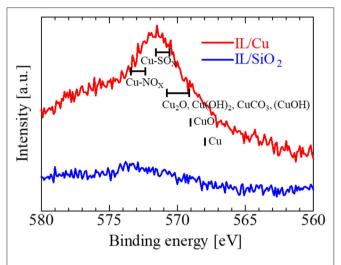

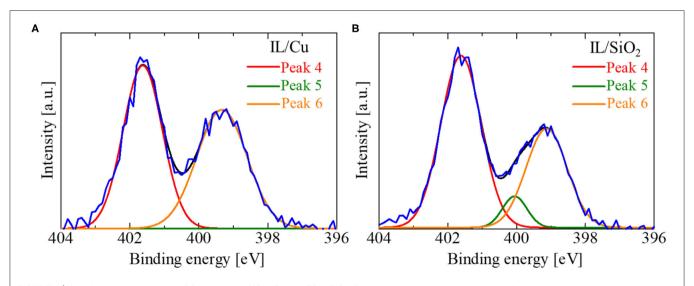

## 39 Memristors With Controllable Data Volatility by Loading Metal Ion-Added Ionic Liquids

Hiroshi Sato, Hisashi Shima, Toshiki Nokami, Toshiyuki Itoh, Yusei Honma, Yasuhisa Naitoh, Hiroyuki Akinaga and Kentaro Kinoshita

## 50 Engineering Tunneling Selector to Achieve High Non-linearity for 1S1R Integration

Navnidhi K. Upadhyay, Thomas Blum, Petro Maksymovych, Nickolay V. Lavrik, Noraica Davila, Jordan A. Katine, A. V. Ievlev, Miaofang Chi, Qiangfei Xia and J. Joshua Yang

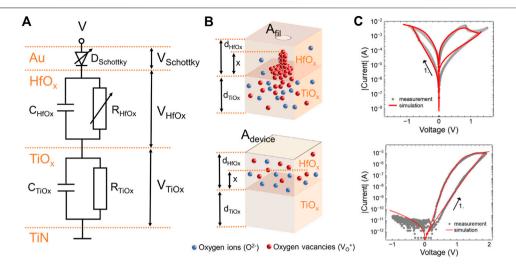

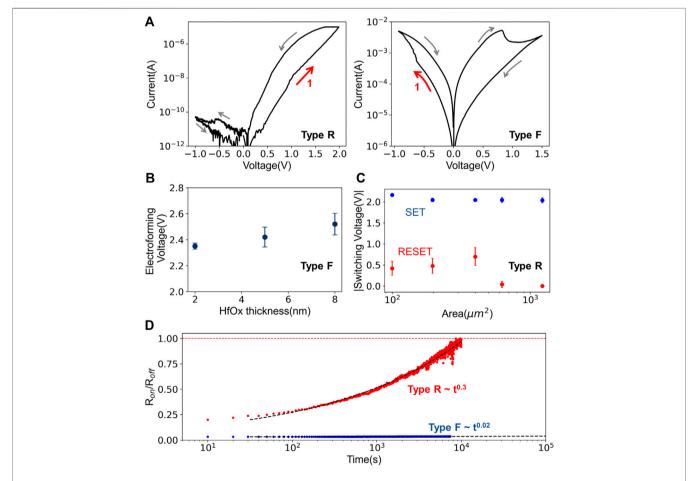

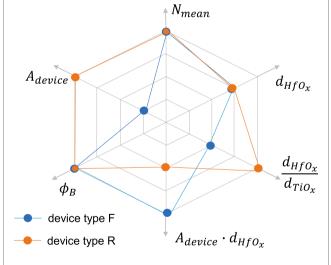

## 60 Engineering Method for Tailoring Electrical Characteristics in TiN/TiO /HfO /Au Bi-Layer Oxide Memristive Devices

Seongae Park, Stefan Klett, Tzvetan Ivanov, Andrea Knauer, Joachim Doell and Martin Ziegler

#### 76 Modeling-Based Design of Memristive Devices for Brain-Inspired Computing Yudi Zhao, Ruiqi Chen, Peng Huang and Jinfeng Kang

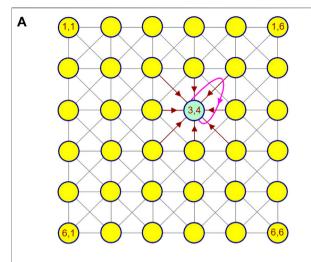

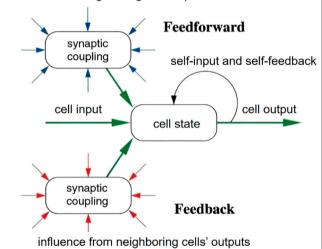

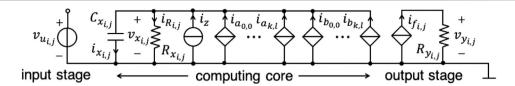

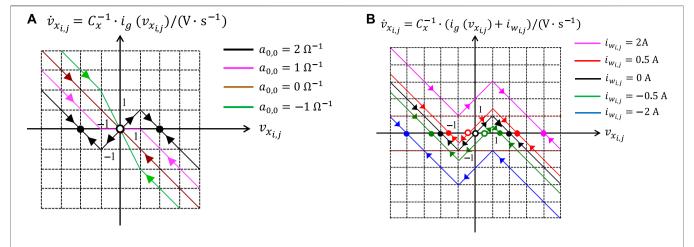

#### 95 System-Theoretic Methods for Designing Bio-Inspired Mem-Computing Memristor Cellular Nonlinear Networks

Alon Ascoli, Ronald Tetzlaff, Sung-Mo Steve Kang and Leon Chua

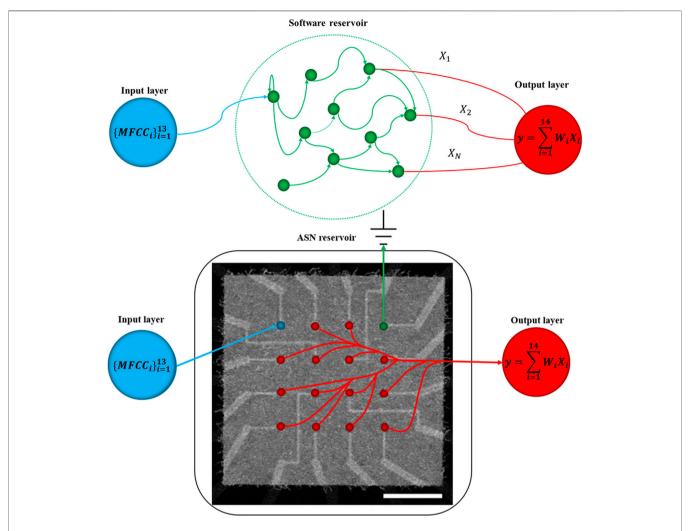

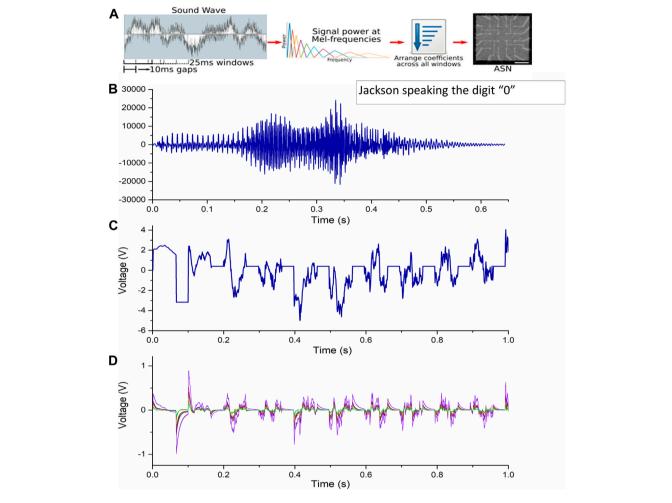

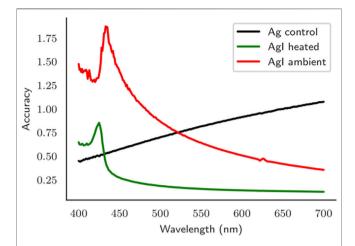

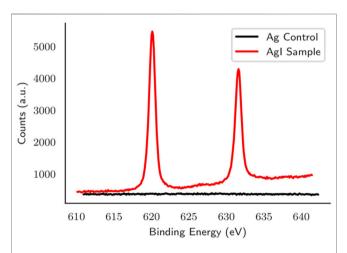

## 128 Spoken Digit Classification by In-Materio Reservoir Computing With Neuromorphic Atomic Switch Networks

Sam Lilak, Walt Woods, Kelsey Scharnhorst, Christopher Dunham, Christof Teuscher, Adam Z. Stieg and James K. Gimzewski

## 139 A Brain-Inspired Homeostatic Neuron Based on Phase-Change Memories for Efficient Neuromorphic Computing

Irene Muñoz-Martin, Stefano Bianchi, Shahin Hashemkhani, Giacomo Pedretti, Octavian Melnic and Daniele Ielmini

#### 153 Memristive Hodgkin-Huxley Spiking Neuron Model for Reproducing Neuron Behaviors

Xiaoyan Fang, Shukai Duan and Lidan Wang

## 171 TCAD Modeling of Resistive-Switching of HfO<sub>2</sub> Memristors: Efficient Device-Circuit Co-Design for Neuromorphic Systems

Andre Zeumault, Shamiul Alam, Zack Wood, Ryan J. Weiss, Ahmedullah Aziz and Garrett S. Rose

### 187 TReMo+: Modeling Ternary and Binary ReRAM-Based Memories With Flexible Write-Verification Mechanisms

Shima Hosseinzadeh, Mehrdad Biglari and Dietmar Fey

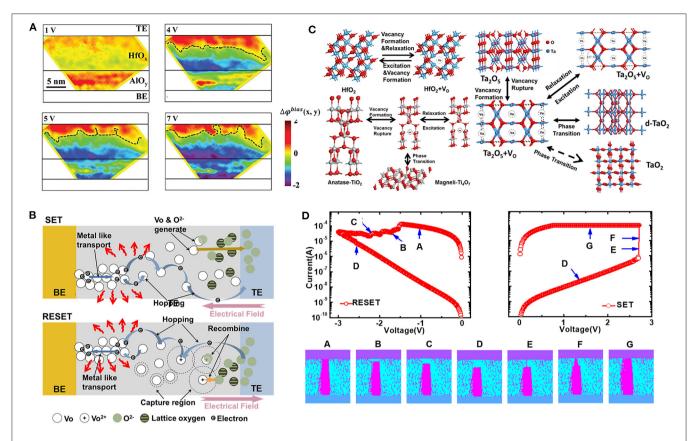

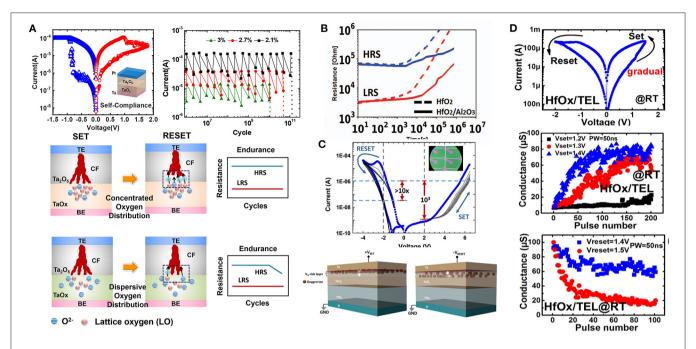

# Investigation on the Stabilizing Effect of Titanium in HfO<sub>2</sub>-Based Resistive Switching Devices With Tungsten Electrode

Vittorio Fra 1,2, Elmira Shahrabi2, Yusuf Leblebici2 and Carlo Ricciardi1\*

<sup>1</sup> Department of Applied Science and Technology (DiSAT), Politecnico di Torino, Turin, Italy, <sup>2</sup> Microelectronic Systems Laboratory (LSM), Swiss Federal Institute of Technology (EPFL), Lausanne, Switzerland

Resistive switching (RS) devices, also referred to as resistive random access memories (ReRAMs), rely on a working principle based on the change of electrical resistance following proper external electrical stimuli. Since the demonstration of the first resistive memory based on a binary transition metal oxide (TMO) enclosed in a metal-insulator-metal (MIM) structure, this class of devices has been considered a key player for simple and low-cost memories. However, successful large-scale integration with standard complementary metal-oxide-semiconductor (CMOS) technologies still needs systematic investigations. In this work, we examine the beneficial effect titanium has when employed as a buffer layer between CMOS-compatible materials like hafnium dioxide and tungsten. Hindering the tungsten oxidation, Ti provides RS stabilization and allows getting faster responses from the devices. Through an extensive comparative study, the effect of both thickness and composition of Ti-based buffer layers is investigated. The reported results show how titanium can be effectively employed to stabilize and tailor the RS behavior of the devices, and they may open the way to the definition of new design rules for ReRAM-CMOS integration. Moreover, the gradual switching and the response speed tunability observed employing titanium might also extend the domain of interest of these results to brain-inspired computing applications.

#### OPEN ACCESS

#### Edited by:

J. Joshua Yang, University of Southern California, Los Angeles, United States

#### Reviewed by:

Massood Atashbar, Western Michigan University, United States Abhay A. Sagade, SRM Institute of Science and Technology, India

#### \*Correspondence:

Carlo Ricciardi carlo.ricciardi@polito.it

#### Specialty section:

This article was submitted to Nanodevices, a section of the journal Frontiers in Nanotechnology

Received: 07 August 2020 Accepted: 29 September 2020 Published: 30 October 2020

#### Citation

Fra V, Shahrabi E, Leblebici Y and Ricciardi C (2020) Investigation on the Stabilizing Effect of Titanium in HfO<sub>2</sub>-Based Resistive Switching Devices With Tungsten Electrode. Front. Nanotechnol. 2:592684. doi: 10.3389/fnano.2020.592684 Keywords: resistive switching, ReRAM, tungsten, titanium, buffer layer

#### INTRODUCTION

Devices with tunable electrical resistance find application in information and communication technologies (ICTs) since the end of the 19th century, when the so-called coherer was employed as receiver in Marconi's wireless telegraph (Marconi, 1899) thanks to the possibility of changing, and retaining, its electrical conductivity upon external stimuli. Some decades later, in the 1960s, attention started focusing on oxide materials with similar properties (Gibbons and Beadle, 1964; Lamb and Rundle, 1967), opening the way for the wide class of devices nowadays identified as resistive memories. Also referred to as resistive random access memories (ReRAMs) or oxide RAMs (OxRAMs), these resistive switching (RS) devices typically rely on a simple metal–insulator–metal (MIM) structure composed of two metallic electrodes enclosing an insulating oxide layer (Waser and Aono, 2007), but similar stacks without metals have been demonstrated too (Yen et al., 2019). As for the coherer, their working principle is based on the change of electrical resistance

as a response to proper external electrical stimuli. The condition of low conductivity is defined as high-resistance state (HRS), and it can be turned into a more conductive low-resistance state (LRS) through the so-called SET process. The opposite transition, resulting in a resistance increase, namely the transition from LRS to HRS, is instead named RESET. When both the state transitions occur with the same polarity, RS devices are classified as unipolar, while they are defined as bipolar if SET and RESET require opposite polarities (Ielmini and Waser, 2016). In most cases, before exhibiting successful switching between these states, RS devices require the so-called forming process, which gives the first transition of the pristine device to a highly conductive state. Since the demonstration of the first resistive memory based on a binary transition metal oxide (TMO) (Baek et al., 2005), this class of devices has been considered a key player for simple and low-cost memories able to compete with the marketleading technologies (Wong et al., 2012; Meena et al., 2014). Such a perspective translated into an unceasing driving force for research efforts to continuously improve features like low power consumption, high density, fast switching, high endurance, long retention, and compatibility with complementary metal-oxidesemiconductor (CMOS) technologies (Cai et al., 2019; Tang et al., 2019; Xia and Yang, 2019; Wang et al., 2020). In seeking to fulfill these requirements, many studies have been carried out on subjects ranging from the physical behavior to the hardware implementation. As a result, it is now well-established that both interface-type (Celano et al., 2017; Govoreanu et al., 2017) and filamentary-type (Joshua Yang et al., 2009; Lee et al., 2009; Celano et al., 2014) resistive switching exist, and it is widely accepted that the formation of a conductive filament involves ion motion within the insulating layer of the MIM structure (Valov, 2014; Sun et al., 2019; Wang et al., 2020). Inmemory computing systems have been shown (Zidan et al., 2018) and brain-inspired functionalities have been demonstrated (Xia and Yang, 2019). Despite these outstanding findings, successful large-scale integration with standard CMOS technologies is only just at the beginning and still needs further systematic investigations able to provide new design rules. In this context, many materials have been studied for both the insulating layer and the electrodes. Silver and copper have been employed in the so-called electrochemical metallization (ECM) memory cells, where they work as electrochemically active electrodes to release cations for metallic filament formation upon electromigration through the "I" layer (Valov et al., 2011). Platinum and titanium nitride have been shown to be suitable for inert electrodes (Tappertzhofen et al., 2014), while oxidizing metals like tungsten, titanium, hafnium, and tantalum have been studied as electrodes in valence change memory (VCM) devices (Chen et al., 2013; Lin et al., 2013; Shahrabi et al., 2019) and many oxides have been tested as an insulating layer. Among them, resounding success has been achieved by HfO<sub>2</sub> (Chen et al., 2009), Ta<sub>2</sub>O<sub>5</sub> (Kim et al., 2016),  $TaO_x$  (Yang et al., 2010),  $TiO_2$  (Chen et al., 2017), and ZnO (Conti et al., 2019). Moreover, it has been pointed out by different works that the whole material stack of each ReRAM cell, and not only the single layers, is the ultimate responsible for the device performances (Gilmer et al., 2011; Walczyk et al., 2012; Chen et al., 2013; Kim et al., 2016; Rahaman et al., 2017; Singh et al., 2018; Ambrosi et al., 2019; Kindsmüller et al., 2019; Lee et al., 2019; Shahrabi et al., 2019). Particularly, in the framework of VCM devices, a key role is played by the interaction between the metal oxide in the "I" layer and the oxidizing electrode. Such devices, indeed, rely on the formation and rupture of a conductive filament resulting from local valence changes of the metal within the oxide, which, in turn, results from the migration of  ${\rm O}^{2-}$  ions and the subsequent formation of oxygen vacancies  $(V_O^2)$  under the action of an applied voltage (Celano et al., 2016). The motion of these species strongly depends on the oxygen exchange between the oxide film and the oxidizing electrode and can be described by the reaction:

$$M \text{ (bulk)} + \text{TMO} \rightleftharpoons MO_x + \text{TMO}_{1-x} + x \cdot V_O^{\cdot \cdot} + 2x \cdot e^{-}$$

(1)

where M is the oxidizing electrode and TMO is the oxide in the "I" layer.

In view of the upcoming CMOS integration, tungsten turns out to be a feasible choice for the oxidizing electrode due to its already established employment for vertical interconnect accesses (VIAs). However, when used in direct contact with an oxide, its multiple and metastable oxide forms introduce relevant instability in the memory cell performances, so that the insertion of a buffer layer becomes necessary (Shahrabi et al., 2019). In order to efficiently mitigate the effect of the non-stable oxides tungsten can form, a suitable candidate to play this role is titanium. Thanks to the lower energy it requires for reaction (1) with respect to tungsten (Guo and Robertson, 2014; Kim et al., 2016), titanium can indeed extract oxygen from the "I" layer more effectively, and so hinder the formation of metastable tungsten oxides. Furthermore, in the perspective of possible future applications and integrations, the strength of titanium as a suitable candidate for buffer layers comes from its capability to allow gradual RESET transitions for multiple resistance levels tuning (Shahrabi et al., 2019).

In this work, a systematic study of the effect of titaniumbased buffer layers enclosed between a tungsten electrode and an oxide layer is carried out on RS devices exhibiting hafnium oxide (HfO<sub>2</sub>) as the insulating layer of the MIM structure and platinum as the inert electrode. The role played by Ti in modulating the interaction between the oxidizing electrode and the oxide is investigated through an extensive, comparative investigation of devices with buffer layers having different thicknesses and different compositions. Devices without a buffer layer, namely with the tungsten electrode in direct contact with the HfO2 film, are also tested and kept as performance references. A clear effect of thickness is observed in both static and dynamic operations, with lower and tunable forming, SET and RESET voltages, better endurance, and faster response achieved through a thicker Tibased buffer layer. Especially, with respect to devices without any buffer layer, the early HRS failure is fixed and pulses down to three orders of magnitude shorter can be employed. These results, coupled with gradual RESET transitions, make the Ti buffer/W electrode stack a versatile candidate for CMOS-compatible ReRAM cells to be employed in brain-inspired applications.

#### **MATERIALS AND METHODS**

#### **Device Fabrication**

For our devices, a cross-point geometry was adopted, with VIA openings defining the active region of the ReRAM cells. Using a standard 4-in. Si wafer with a 500-nm-thick SiO2 layer as a substrate, platinum electrodes were first defined, starting with sputtering deposition of a 5-nm-thick titanium adhesion layer and a 125-nm-thick Pt film by a Pfeiffer Spider 600. Patterning was then performed through photolithography and dry etching, carried out with an STS Multiplex ICP etcher. Afterwards, in order to assure electrical isolation between the electrodes, a 100-nm-thick low thermal oxide (LTO) was deposited at 425°C by means of low-pressure chemical vapor deposition (LPCVD). Once the Pt electrodes were patterned and isolated, VIA openings of different sizes were defined across the LTO passivation layer performing photolithography and buffer oxide etch (BOE). Thereafter, HfO2 and the Ti-based buffer layers were deposited, the latter with thickness varying sample by sample (1, 3, and 5 nm) and the former always 5 nm thick. Concerning the oxide, atomic layer deposition (ALD) at 200°C was performed by means of a BENQ TFS200, while the buffer layers were deposited by room temperature sputtering, with an Alliance Concept DP650, employing two different targets: pure titanium (99.995%) and mixed titanium-tungsten (99.99% of purity with 10% in weight of Ti). By means of the same sputtering tool, the tungsten electrode and a titanium nitride capping layer were then deposited, with thicknesses of 60 and 15 nm, respectively. Finally, to pattern the electrode and define the arrays of cross-point cells, photolithography and dry etching were performed, employing again the STS Multiplex ICP dry etcher.

#### **Device Characterization**

The device characterization was carried out through electrical tests in three different configurations, all of them performed in air at room temperature. DC sweeping mode was first adopted to evaluate the forming voltage and to inspect the cycling operation. To this aim, a parameter analyzer (Agilent B1500) was employed, applying voltage ramps at the tungsten electrode and keeping grounded the platinum one. During these measurements, a compliance current,  $I_{\rm CC}$ , intended to prevent irreversible damages to the devices, was imposed through the internal modules of the characterization tool. Pulse measurements were instead performed to test the dynamic behavior in terms of endurance, response speed, and retention.

In this case, since parameter analyzers generally suffer from pure accuracy in current limitation due to a certain delay with respect to the characteristic times of forming and SET processes (Tirano et al., 2011; Nafria et al., 2017), an external n-channel transistor (n-MOSFET) was used to control the compliance current. The device under test was connected in series to the drain of the transistor (bit line), while the source (source line) was grounded and voltages were applied at the gate (word line) to adjust the current limitation. Additionally, conductive atomic force microscopy (C-AFM), by an Asylum Research Cipher VRS, was employed to investigate the forming process directly probing the HfO<sub>2</sub> layer on top of the W/Ti buffer/HfO<sub>2</sub> stacks. Full-platinum AFM tips from Rocky Mountain Nanotechnologies were used as the top electrode in order to reproduce the same MIM structure as for the cross-point cells characterized by means of the parameter analyzer.

#### **RESULTS**

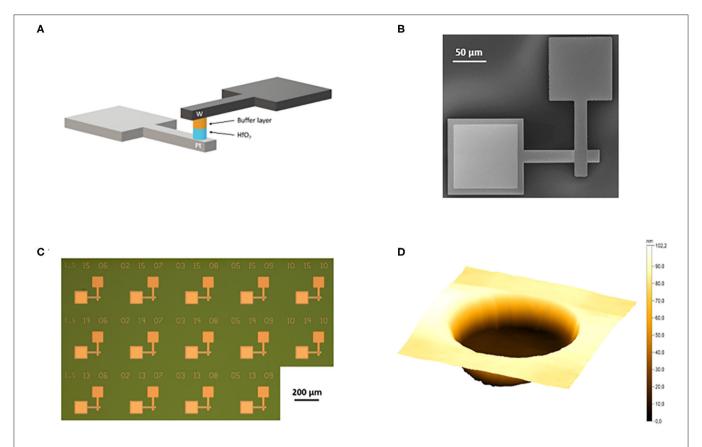

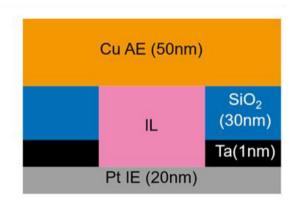

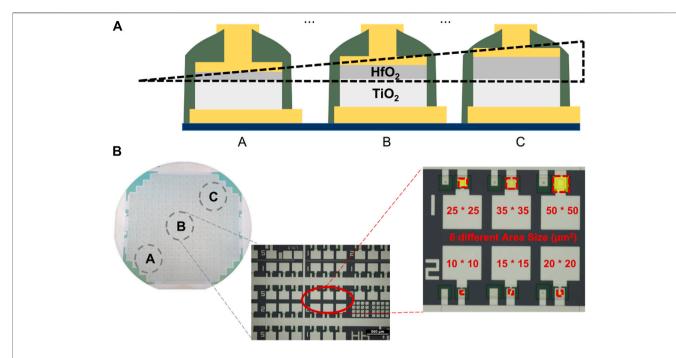

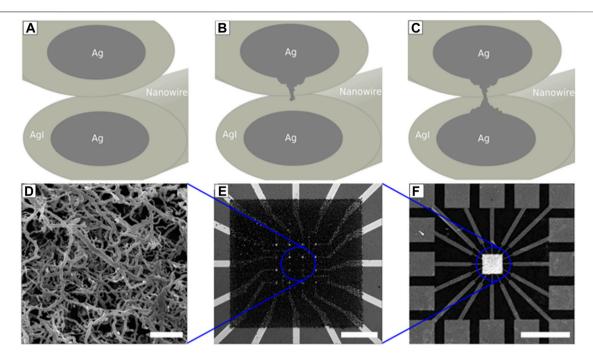

All the different stacks employed for the tested devices are summarized in **Table 1**. A 3D sketch of the device structure is then reported in **Figure 1A**, while the field emission scanning electron microscope (FESEM) image in **Figure 1B** shows the actual geometry with a top view of a single ReRAM cell. The micrograph in **Figure 1C** highlights the periodic arrangement of the devices adopted on each sample, with the different VIA diameters of 1.5, 2, 3, 5, and 10 μm. A topography image acquired by AFM in contact mode is also reported in **Figure 1D**, where a 10-μm VIA is shown.

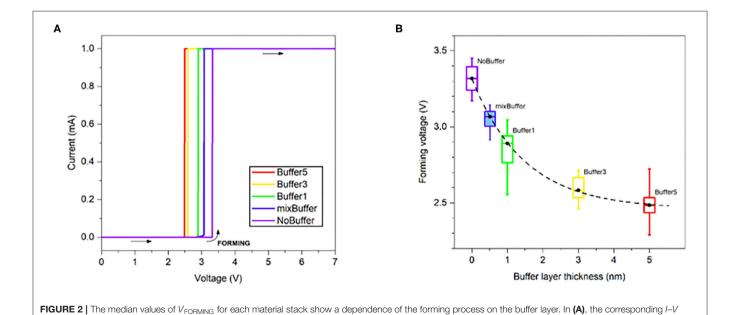

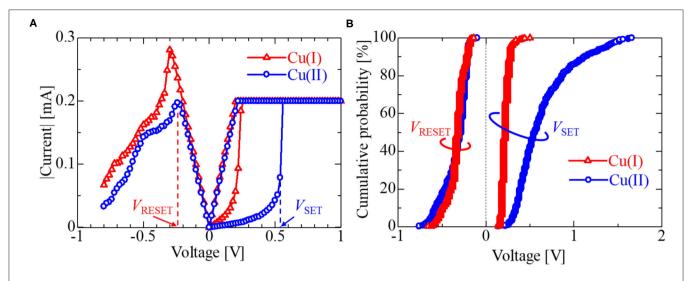

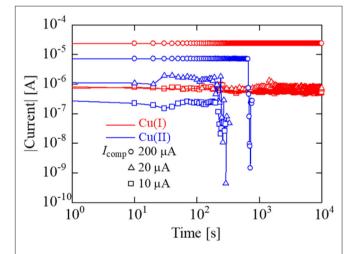

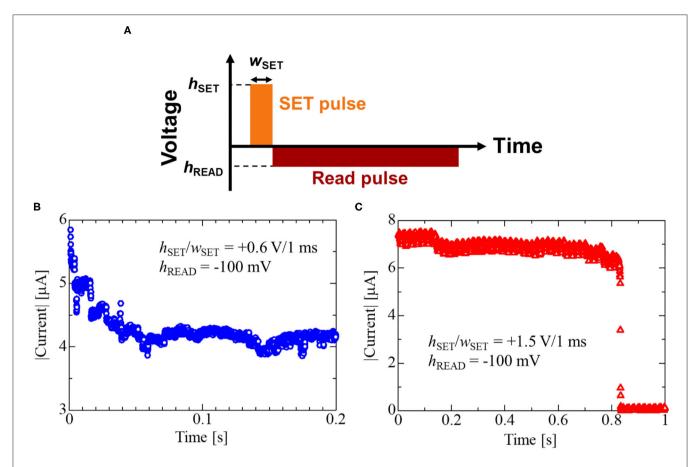

In order to carry out a complete performance analysis suited to compare the material stacks and investigate the effect of the Tibased buffer layers, 25 devices for each sample were first subjected to a systematic DC characterization made of forming and cycling steps. Pristine devices underwent positive voltage sweeps from 0 to 7 V with a compliance current of 1 mA; then, bipolar voltage ramps ranging from  $-1.5 \, \text{V}$  to 3 V were applied to the same devices to test the cycling behavior. Bipolar resistive switching, with SET and RESET occurring in positive and negative polarity, respectively, was observed for all the devices regardless of the material stack. The latter, conversely, turned out to play a role in the definition of the device performance. First of all, an impact of the titanium-based buffer layers on the forming process was observed, with a decrease of the forming voltage ( $V_{\text{FORMING}}$ ) for thicker buffer layers (**Figure 2A**). Particularly, as presented

**TABLE 1** | Material stacks of all the tested devices.

| Sample name | Inert electrode |                | Oxide layer      |                | Buffer layer |                | Oxidizing electrode |                |

|-------------|-----------------|----------------|------------------|----------------|--------------|----------------|---------------------|----------------|

|             | Material        | Thickness (nm) | Material         | Thickness (nm) | Material     | Thickness (nm) | Material            | Thickness (nm) |

| noBuffer    | Pt              | 125            | HfO <sub>2</sub> | 5              | _            | -              | W                   | 60             |

| mixBuffer   | Pt              | 125            | HfO <sub>2</sub> | 5              | W:Ti 10%     | 3              | W                   | 60             |

| Buffer1     | Pt              | 125            | HfO <sub>2</sub> | 5              | Ti           | 1              | W                   | 60             |

| Buffer3     | Pt              | 125            | HfO <sub>2</sub> | 5              | Ti           | 3              | W                   | 60             |

| Buffer5     | Pt              | 125            | HfO <sub>2</sub> | 5              | Ti           | 5              | W                   | 60             |

FIGURE 1 | The cross-point geometry of the tested devices is shown through a 3D sketch (A) and a field emission scanning electron microscope (FESEM) image in top view (B). In the first case, the schematic, not to scale, focuses on a single device emphasizing the material stack, while in the second picture the actual geometry is shown. The periodic arrangement of the resistive random access memory (ReRAM) cells with all the different vertical interconnect access (VIA) dimensions is then highlighted by a micrograph (C). In (D), a single VIA with a diameter of 10 μm is shown by a topography image obtained with contact mode atomic force microscopy (AFM).

characteristics are shown, while in (B) their exponential decay as a function of the Ti-based buffer layer thickness is presented.

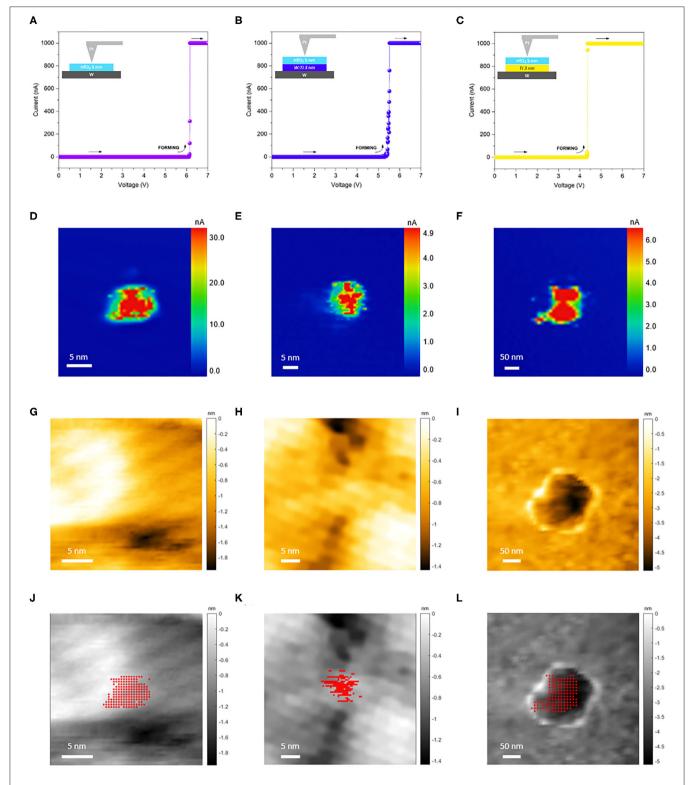

**FIGURE 3** Investigation of the forming process was performed with conductive atomic force microscopy (C-AFM) directly probing the oxide layer by means of full-platinum tips. The resulting I-V characteristics are reported in **(A-C)**, where  $V_{\text{FORMING}}$  is reported to decrease with increasing amount of titanium in the buffer layer. In **(D-F)**, the current maps acquired after the forming process are reported, with conductive spots clearly shown for all the tested material stacks. The topography images obtained at the same time with the current maps are then reported in **(G-I)**, showing the presence of morphological changes in the case of the Buffer3 samples **(I)**. In **(J-L)**, the superposition of topographical and electrical images is presented.

by the box plot in **Figure 2B**, such a reduction turned out to be well-described by an exponential decay of the median values of  $V_{\rm FORMING}$  for the samples with pure Ti buffer layers. The same curve was then employed, the other way around, to define an effective thickness of the mixed buffer layer, which came out to be about 0.5 nm. Such an effective thickness, smaller than the real one of 3 nm, clarifies that the key player in the reduction of the forming voltage is not properly the thickness of the buffer layer but rather the presence, and the amount, of titanium between the hafnium dioxide film and the tungsten electrode.

Consistent results were shown by the C-AFM characterization too. As reported in Figures 3A-C, three different stacks were investigated, namely NoBuffer, mixBuffer, and Buffer3, with the structure sketched in the insets of Figures 3A-C. As is clear from those pictures, the same MIM geometry as the one schematized in Figure 1A was reproduced thanks to the full-platinum AFM tip, which played the role of the inert electrode. By selecting such triplet of stacks, the key points of the previous analysis were further investigated. Indeed, with this set of devices, two main comparisons were possible, namely (i) the case with or without the buffer layer and (ii) the case of pure or mixed titanium with a fixed thickness. For each sample investigated by means of C-AFM, forming was induced first and current maps were produced afterwards. For both the measurements, the platinum tip was kept grounded and voltages were applied at the tungsten electrode. To achieve forming, voltage sweeps from 0

to 7 V were employed as for the analysis carried out through the parameter analyzer, with a current compliance set at 1  $\mu$ A. Current maps were instead produced applying fixed voltages. Similarly to Figures 2A, 3A-C show a reduction of  $V_{\text{FORMING}}$ depending on the presence of titanium between the oxidizing electrode and the oxide layer. Furthermore, in accordance with Figure 2B, such a reduction turned out to be related to the amount of titanium in the buffer layer rather than to the physical thickness of the Ti-based layer only. Indeed, both the buffer layers employed for the mixBuffer and Buffer3 samples are 3 nm thick, but their compositions differ from one another, with the mixBuffer sample exhibiting a tungsten film with 10% in weight of titanium instead of a pure Ti film. The current maps, produced after forming was induced, are then reported in Figures 3D-F. They show a nanometer-sized conductive spot for each sample, which strongly suggests a filamentary nature of the resistive switching in the tested devices. The topography images, acquired simultaneously with the creation of the current maps, are reported too (Figures 3G-I), and a superposition of the current maps on the topography images is presented in Figures 3J-L as the result of a point-by-point analysis of the electrical conduction. Particularly, in the case of Buffer3 samples, the presence of morphological changes is reported (Figure 3I), and Figure 3L highlights that such modifications turn out to perfectly match with the conductive spot found in the current map.

FIGURE 5 | Applying bipolar voltage sweeps, the switching behavior of the tested device was investigated through the resulting I-V characteristics. The reported graphs are representative curves for each material stack. In the NoBuffer samples (A), current fluctuations occur before the SET process and RESET takes place abruptly. A similar behavior is shown by the mixBuffer (B) and Buffer1 (C) samples also. In the Buffer3 (D) and Buffer5 (E) samples, instead, the current fluctuations in the high-resistance state (HRS) in positive polarity are not observed; a lower  $V_{\text{SET}}$  is found and gradual RESET occurs as it is flagged by a smooth current decrease for negative voltages close to  $V_{\text{RESET}}$ .

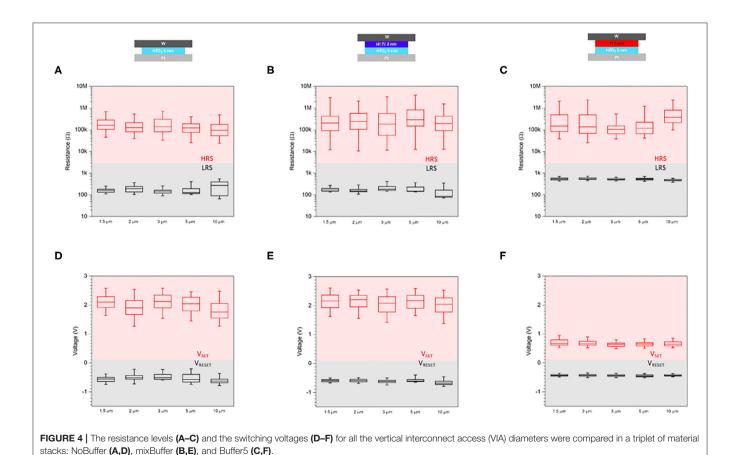

Even though the C-AFM analysis clearly reported the presence, in all the tested material stacks, of conductive spots at the HfO2/Pt interface, suggesting resistive switching of filamentary type, a statistical DC characterization was performed to exclude a dependence of the RS on the device area as a consequence of interfacial effects at the W/HfO2 or buffer layer/HfO2 interface. By means of the parameter analyzer, bipolar voltage sweeps in the range -1.5 to 3 V were applied on 25devices for the NoBuffer, mixBuffer, and Buffer5 samples. As summarized by the box plots in Figure 4, such characterization revealed that RS parameters like the resistance levels, V<sub>SET</sub>, and  $V_{\text{RESET}}$  are independent of the device area since no correlation was found between these quantities and the diameter of the VIAs (1.5, 2, 3, 5, and 10 µm). Therefore, we can conclude that the observed resistive switching can be truly ascribed to a filamentary mechanism.

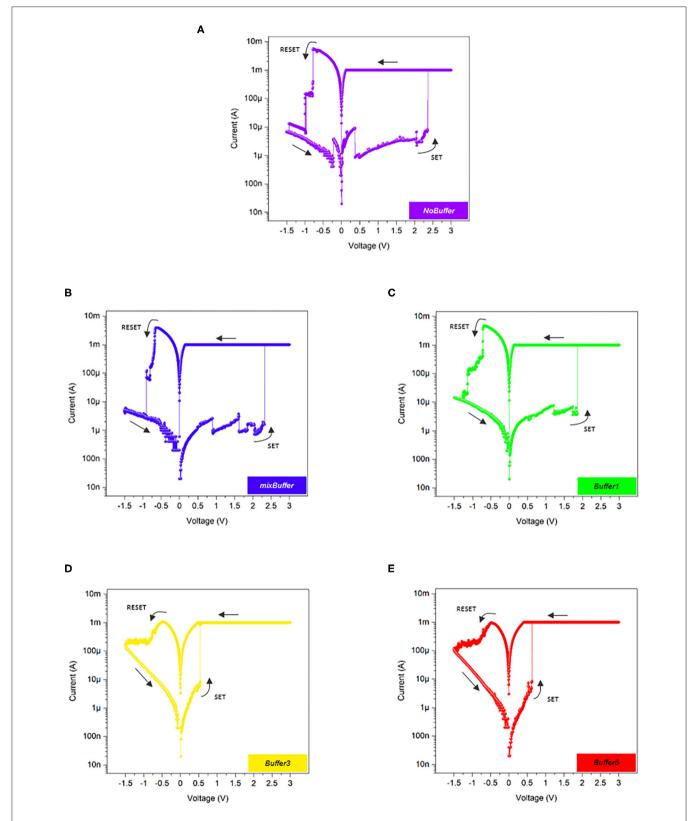

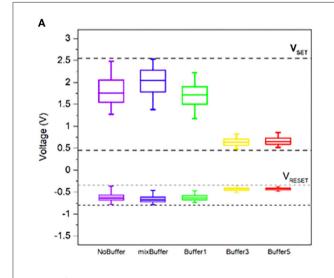

Through the same DC characterization, that is to say applying consecutive cycles of bipolar voltage sweeps  $0 \text{ V} \rightarrow -1.5 \text{ V} \rightarrow 3 \text{ V}$  $\rightarrow$  0 V, the switching behavior of the devices was investigated. As is reported in **Figure 5**, where I-V characteristics representative of a typical cycle for each material stack are shown, two different behaviors can be highlighted in the DC operation regime for Ti-based buffer layers thinner or thicker than 3 nm, respectively. More in detail, starting from Figure 5A, which reports the cycling behavior of the devices with no buffer layer, clear current fluctuations can be appreciated in the HRS for positive voltages. Interpreted from a different, but complementary, perspective, Figure 5A shows that the devices without a buffer layer exhibit some instability during the SET process, with sharp transitions from HRS to LRS occurring at relatively high voltages only after quick, repeated current variations. A similar behavior can be observed in the case of the mixBuffer (Figure 5B) and Buffer1 (Figure 5C) samples too, while a clear change occurs in the Buffer3 (Figure 5D) and Buffer5 (**Figure 5E**) samples. The latter two, indeed, still exhibit abrupt switching from HRS to LRS, but the sharp transition takes place at lower voltages and the I-V characteristics in HRS in positive polarity are much more stable, with no fluctuations. Moreover, as is graphically summarized in **Figure 6A**, which reports the statistical variations of  $V_{\rm SET}$  and  $V_{\rm RESET}$  obtained from the DC characterization, such improved stability in the device operation is coupled to a significantly reduced device-to-device variability.

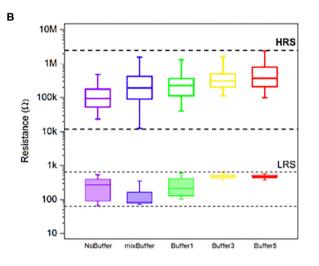

The second major result arising from the insertion of a Tibased buffer layer, which becomes apparent for Buffer3 and Buffer5 samples as for the HRS stability above-mentioned, involves the opposite polarity and the opposite transition. In Figures 5D,E, indeed, a fairly different behavior in the transition from LRS to HRS can be appreciated, with a gradual resistance variation instead of an abrupt switch. Interestingly, such change does not reflect into an increased device stability or reduced device-to-device variability. As reported in Figure 6A, indeed, differently from  $V_{\text{SET}}$ , the RESET voltage does not significantly vary neither from a device to another nor from a sample to another. Similar observations can be made for the resistance values also, whose statistical analysis is reported in Figure 6B. In this case, the effect of Ti-based buffer layers as a stabilizer can be appreciated looking at the variability of the LRS in the different samples. As is clear from the box plot, the resistance value of the highly conductive state is significantly more stable in Buffer3 and Buffer5 samples, while a relevant device-to-device variability affects the devices based on the other material stacks.

The statistical parameters resulting from the DC characterization performed on a total of 125 devices are summarized in **Table 2**.

Based on reaction (1), both the current fluctuations before SET occurs and the gradual RESET can be interpreted referring to oxygen exchanges, which, in turn, involve the oxidizing activity

**FIGURE 6** | The statistical analysis of the DC characterization performed on 25 devices for each material stack is presented by means of box plots. In **(A)**, the switching voltages are reported, while the resistance levels are shown in **(B)**. In both cases, for the sake of clarity, dashed lines are employed to distinguish the different ranges of data.

**TABLE 2** | Median values and standard deviations from the statistical DC characterization.

| Sample name | V <sub>FORMIN</sub> | <sub>IG</sub> (V) | V <sub>SET</sub> | (V)  | V <sub>RESET</sub> | (V)  | HRS    | i (kΩ)  | LRS    | S (Ω)  |

|-------------|---------------------|-------------------|------------------|------|--------------------|------|--------|---------|--------|--------|

|             | Median              | SD                | Median           | SD   | Median             | SD   | Median | SD      | Median | SD     |

| noBuffer    | 3.31                | 0.09              | 1.76             | 0.38 | -0.64              | 0.12 | 94.48  | 154.61  | 272.55 | 171.05 |

| mixBuffer   | 3.07                | 0.08              | 2.05             | 0.34 | -0.68              | 0.10 | 192.86 | 3711.84 | 84.86  | 84.86  |

| Buffer1     | 2.89                | 0.15              | 1.72             | 0.32 | -0.63              | 0.09 | 226.78 | 427.42  | 214.86 | 169.08 |

| Buffer3     | 2.58                | 0.09              | 0.64             | 0.10 | -0.43              | 0.04 | 309.41 | 499.79  | 483.00 | 77.28  |

| Buffer5     | 2.49                | 0.12              | 0.65             | 0.10 | -0.43              | 0.03 | 368.39 | 1011.09 | 474.82 | 69.09  |

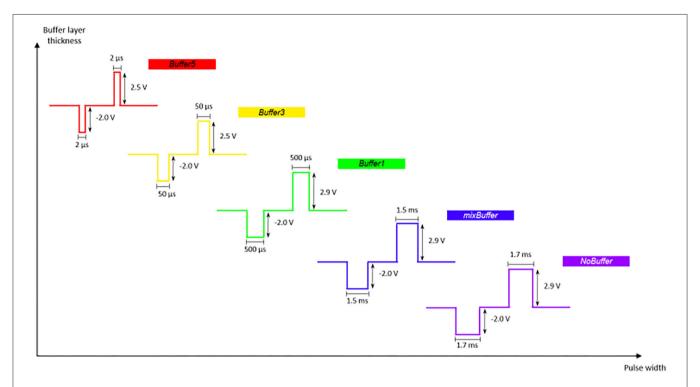

FIGURE 7 | The insertion of buffer layers with increasing amount of titanium translates into a faster response of the devices, as shown by the pulse width reduction achieved with thicker Ti-based buffer layers.

of the layers in contact with the hafnium dioxide. Since, as already mentioned, one of these layers is always made of platinum, which is inert, the two phenomena must be related to the buffer layer, or to the tungsten electrode when the former is not present. In this view, the interpretation of the observed behavior in the DC regime can be traced back to the different oxidizing characteristics of titanium and tungsten. Current fluctuations may be related to the multiple, metastable oxides tungsten can form before reaching the stable WO3 (Lassner and Schubert, 1999; Shahrabi et al., 2019) since the emergence of such fluctuations can be appreciated in the NoBuffer, mixBuffer, and Buffer1 samples only. In the Buffer3 and Buffer5 samples, indeed, the thickness of the buffer layers is such that a large enough amount of titanium is present to effectively hinder the formation of metastable tungsten oxides (Shahrabi et al., 2019). On the other hand, concerning the transition from an abrupt to a gradual RESET, similar arguments hold, and the smoother resistance change can be again ascribed to the oxidizing behavior of the buffer layer. The gradual transition, indeed, takes place in the Buffer3 and Buffer5 samples only, that is to say, once more, only in those devices with a large enough amount of titanium between the tungsten electrode and the hafnium dioxide.

A further confirmation of the stabilizing effect given by the titanium buffer layer was then found with pulse tests aimed at investigating the endurance of the devices, namely their cycling reliability. For each material stack, an initial optimization procedure was first performed on the pulse parameters in order to find the best combinations of pulse width and pulse amplitude. As is shown in **Figure 7**, pulses were optimized for both SET and RESET since, as shown by the DC characterization, the bipolar RS of the tested devices is not symmetrical. Specifically,  $|V_{\rm SET}|$  turned out to be higher than  $|V_{\rm RESET}|$ , while identical pulse widths were used in both polarities. Finally, a delay of 200 ms was always employed between a pulse and the following one.

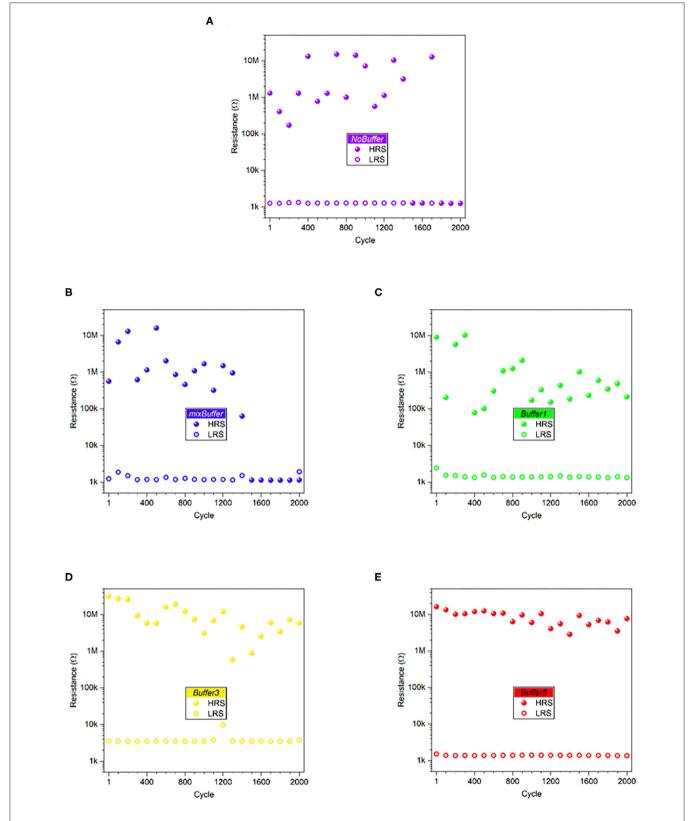

FIGURE 8 | Endurance tests were performed with a fixed sequence of 2,000 SET-RESET pulse pairs. The NoBuffer (A) and mixBuffer (B) samples showed high-resistance state (HRS) failure after about 1,500 cycles, while the devices from the other material stacks (C-E) successfully completed the fixed-length test. Additionally, a stabilization of the HRS was observed for the Buffer1 (C), Buffer3 (D), and Buffer5 (E) samples.

**TABLE 3** | Summary of resistance values during endurance and retention measurements.

| Sample name |           | Endurance                |           |                          |           | Retention                |           |                             |

|-------------|-----------|--------------------------|-----------|--------------------------|-----------|--------------------------|-----------|-----------------------------|

|             |           | HRS                      |           | LRS                      | Н         |                          | IRS LRS   |                             |

|             | Mean (MΩ) | Relative uncertainty (%) | Mean (kΩ) | Relative uncertainty (%) | Mean (MΩ) | Relative uncertainty (%) | Mean (kΩ) | Relative<br>uncertainty (%) |

| noBuffer    | 4.73      | 119                      | 1.27      | 1.4                      | 13.22     | 30                       | 1.47      | 4.8                         |

| mixBuffer   | 3.10      | 156                      | 1.27      | 18                       | 1.26      | 2.0                      | 1.00      | 2.3                         |

| Buffer1     | 1.61      | 180                      | 1.44      | 16                       | 0.93      | 2.9                      | 1.35      | 2.3                         |

| Buffer3     | 10.11     | 87                       | 3.81      | 36                       | 32.26     | 3.3                      | 2.52      | 3.9                         |

| Buffer5     | 8.52      | 41                       | 1.38      | 2.3                      | 17.02     | 5.1                      | 1.27      | 6.3                         |

HRS, high-resistance state; LRS, low-resistance state.

**Figure 7** clearly shows that such an optimization revealed a key impact of titanium on the dynamical operation regime of the tested devices. Indeed, besides the reduction of pulse amplitude needed for successful RS, which was already pointed out with the DC characterization, pure Ti buffer layers turned out to lead to a pulse width reduction down to three orders of magnitude with respect to the devices without a buffer layer.

Once the pulse parameter optimization was completed, a common test procedure was defined and adopted for all the material stacks, so that a clear performance comparison among the different samples was possible. Specifically, all the devices subjected to the endurance test were subjected to 2,000 SET-RESET pulse pairs aimed at continuously switching between HRS and LRS. The results of this characterization, reported in Figure 8, show how, besides improving the device stability, pure Ti buffer layers also have a beneficial effect on the endurance itself. Figures 8A,B, indeed, reveal that the NoBuffer and mixBuffer samples suffered for HRS failures preventing them from reaching the common test length of 2,000 cycles. Particularly, the devices from both material stacks were not able to overcome 1,500 cycles. Conversely, the Buffer1, Buffer3, and Buffer5 samples were all able to reach the fixed benchmark of 2,000 cycles, thus demonstrating an improvement of about 30%. Moreover, as already mentioned, the stability of the devices significantly improved, as is highlighted in Figures 8C-E by the much less scattered data as the amount of titanium in the buffer layers increases. A quantitative evaluation of the data dispersion can be made through the relative uncertainty (Table 3), which, in the case of HRS, turns out to be smaller than 100% for the Buffer3 and Buffer5 samples only. In more detail, such samples provide relative uncertainties of 87 and 41%, respectively, while 119% is found for the NoBuffer samples, 156% in the case of the mixBuffer ones, and 180% for the devices coming from the Buffer1 samples. The relative uncertainties are instead much smaller for the LRS during the endurance tests, and they do not show any trend related to the material stack.

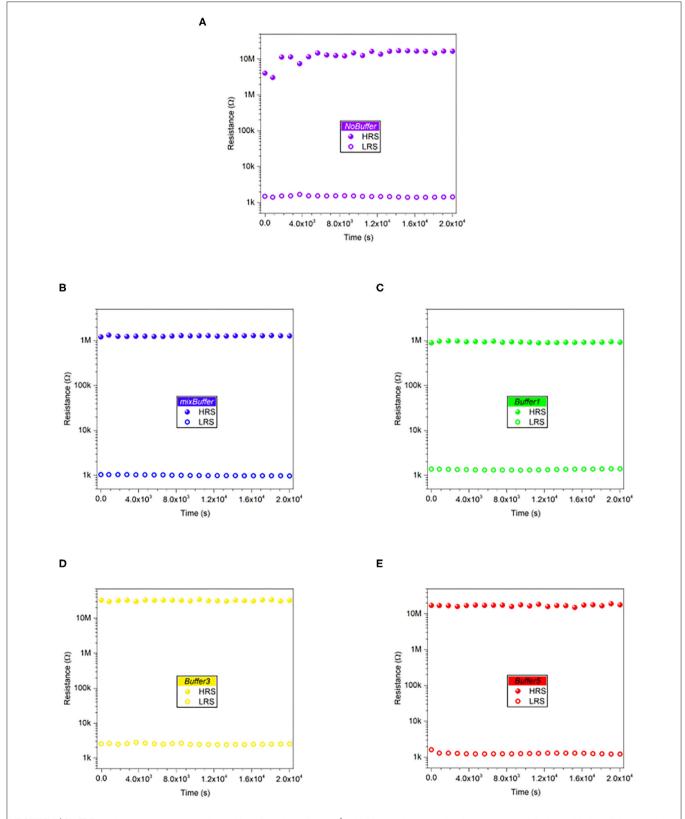

To complete the set of electrical characterizations, retention tests were performed on new samples to compare the capability of the different material stacks of preserving each resistance state. A summary of the mean values, together with their relative uncertainties, for both HRS and LRS during pulse operations

is presented in Table 3. As for the endurance, a common benchmark was set for the retention tests too, and  $2 \times 10^4$  s was adopted as the fixed length for the measurements in order to define a standard procedure for all the samples. The results are shown in Figure 9, where a good stability is reported for all the material stacks. In this case, no significant difference can be appreciated depending on the buffer layer, with all the devices able to reach the fixed value of  $2 \times 10^4$  s and small relative uncertainties on the resistance values, in both HRS and LRS. As a consequence, the retention tests, which rely on the stability of the conductive filament rather than on its formation and rupture, seem to suggest that the Ti-based buffer layers actively play a role only when oxygen exchanges, as in reaction (1), occur, while they remain silent otherwise. The performance tunability and improvement titanium allows to achieve can hence be directly related to the stabilization of the interactions between the oxidizing electrode and the oxide layer. Compared to tungsten, titanium indeed requires a much lower energy to create oxygen vacancies in HfO2, and this significantly hinders the slower tungsten oxidation (Kim et al., 2016). As a consequence, titanium efficiently mitigates the fluctuations induced by the formation of metastable tungsten oxides (Lassner and Schubert, 1999) and allows faster responses from the devices.

#### DISCUSSION

With this work, we have shown how titanium can be employed, as a buffer layer, to stabilize and tune the RS performances of ReRAM cells based on CMOS-compatible materials like HfO2 and tungsten. With an extensive, systematic approach, 125 devices with different material stacks have been tested. Investigating different thicknesses and compositions of the Tibased films, a dependence of the device performances on the buffer layer properties was found, and the amount of titanium in the buffer layer turned out to play a key role. The presented results can be ascribed to the different oxidizing characteristics of titanium and tungsten. The latter, indeed, suffers from a relatively slower oxidation process, producing a variety of metastable oxides, responsible for the RS instability which clearly appears in both DC switching and pulse operations. Employing buffer

**FIGURE 9 | (A–E)** Retention measurements, performed for a fixed time of  $2 \times 10^4$  s, highlighted that a good resistance state stability is provided by all the material stacks, with no significant contribution given by titanium.

layers with a high enough amount of titanium, relevant changes in the device performances have been reported. More in detail, the response speed has been shown to significantly increase according to the pulse width reduction of three orders of magnitude; an improvement of about 30% has been achieved in terms of endurance performance, and an increased stability of the resistance states, especially the HRS, has been obtained in the dynamic operation regime. In light of these results, the Ti buffer/W stack turns out to be a suitable choice for CMOS-compatible ReRAM cells that have to solve reliability issues coming from tungsten electrodes. Furthermore, the possibility of tuning the device performances according to the Ti-based buffer layer properties may open the way to the definition of new design rules for ReRAM integration with standard CMOS technology.

#### **DATA AVAILABILITY STATEMENT**

The raw data supporting the conclusions of this article will be made available by the authors, without undue reservation.

#### **REFERENCES**

- Ambrosi, E., Bricalli, A., Laudato, M., and Ielmini, D. (2019). Impact of oxide and electrode materials on the switching characteristics of oxide ReRAM devices. *Faraday Discuss.* 213, 87–98. doi: 10.1039/C8FD00106E

- Baek, I. G., Lee, M. S., Sco, S., Lee, M. J., Seo, D. H., Suh, D.-S., et al. (2005). "Highly scalable non-volatile resistive memory using simple binary oxide driven by asymmetric unipolar voltage pulses," in *IEDM Technical Digest. IEEE International Electron Devices Meeting*, 2004. (San Francisco, CA), 587–590.

- Cai, F., Correll, J. M., Lee, S. H., Lim, Y., Bothra, V., Zhang, Z., et al. (2019). A fully integrated reprogrammable memristor–CMOS system for efficient multiply–accumulate operations. *Nat. Electron* 2, 290–299. doi:10.1038/s41928-019-0270-x

- Celano, U., Fantini, A., Degraeve, R., Jurczak, M., Goux, L., and vandervorst, W. (2016). Scalability of valence change memory: from devices to tip-induced filaments. AIP Adv. 6:085009. doi: 10.1063/1.4961150

- Celano, U., Gastaldi, C., Govoreanu, B., Richard, O., Bender, H., Goux, L., et al. (2017). Evidences of areal switching in vacancy-modulated conductive oxide (VMCO) memory. *Microelectron. Eng.* 178, 122–124. doi:10.1016/j.mee.2017.04.046

- Celano, U., Goux, L., Belmonte, A., Opsomer, K., Franquet, A., Schulze, A., et al. (2014). Three-dimensional observation of the conductive filament in nanoscaled resistive memory devices. *Nano Lett.* 14, 2401–2406. doi:10.1021/nl500049g

- Chen, Y., Li, L., Yin, X., Yerramilli, A., Shen, Y., Song, Y., et al. (2017). Resistive switching characteristics of flexible TiO2 thin film fabricated by deep ultraviolet photochemical solution method. *IEEE Electron Device Lett.* 38, 1528–1531. doi: 10.1109/LED.2017.2756444

- Chen, Y. S., Lee, H. Y., Chen, P. S., Gu, P. Y., Chen, C. W., Lin, W. P., et al. (2009). "Highly scalable hafnium oxide memory with improvements of resistive distribution and read disturb immunity," in *Tech Dig Int Electron Devices Meet IEDM* (Baltimore, MD), 105–108. doi: 10.1109/IEDM.2009.5424411

- Chen, Y. Y., Goux, L., Clima, S., Govoreanu, B., Degraeve, R., Kar, G. S., et al. (2013). Endurance/retention trade-off on HfO2/Metal Cap 1T1R Bipolar RRAM. *IEEE Trans. Electron Device* 60, 1114–1121. doi: 10.1109/TED.2013.2241064

- Conti, D., Laurenti, M., Porro, S., Giovinazzo, C., Bianco, S., Fra, V., et al. (2019). Resistive switching in sub-micrometric ZnO polycrystalline films. *Nanotechnology* 30:065707. doi: 10.1088/1361-6528/aaf261

- Gibbons, J. F., and Beadle, W. E. (1964). Switching properties of thin NiO films. Solid State Electron 7, 785–790. doi: 10.1016/0038-1101(64)90131-5

#### **AUTHOR CONTRIBUTIONS**

VF and ES contributed to the design and fabrication of the devices. VF performed device characterization. VF and CR wrote and revised the manuscript. CR and YL helped with supervision. All authors contributed to the article and approved the submitted version.

#### **FUNDING**

This research was partially supported by Compagnia di San Paolo through the project for internationalization of research of Politecnico di Torino.

#### **ACKNOWLEDGMENTS**

The help and the technical support given by the staff of the Center of Micro-nano Technology (CMi) of EPFL are gratefully acknowledged. A hearthfelt thank goes to P. Charpilloz for his supervision during AFM measurements.

- Gilmer, D. C., Bersuker, G., Park, H. Y., Park, C., Butcher, B., Wang, W., et al. (2011). "Effects of RRAM stack configuration on forming voltage and current overshoot," in 2011 3rd IEEE Int Mem Work IMW (Monterey, CA), 1–4. doi: 10.1109/IMW.2011.5873225

- Govoreanu, B., Redolfi, A., Zhang, L., Adelmann, C., Popovici, M., Clima, S., et al. (2017). "Vacancy-modulated conductive oxide resistive RAM (VMCO-RRAM): an area-scalable switching current, self-compliant, highly nonlinear and wide on/off-window resistive switching cell," in 2013 IEEE International Electron Devices Meeting (Washington, DC: IEEE), 10.2.1–10.2.4.

- Guo, Y., and Robertson, J. (2014). Materials selection for oxide-based resistive random access memories. *Appl. Phys. Lett.* 105:223516. doi: 10.1063/1.4903470

- Ielmini, D., and Waser, R. (2016). Resistive Switching. Weinheim, Germany: Wiley-VCH Verlag GmbH & Co. KGaA. doi: 10.1002/9783527680870

- Joshua Yang, J., Miao, F., Pickett, M. D., Ohlberg, D. A. A., Stewart, D. R., Lau, C. N., et al. (2009). The mechanism of electroforming of metal oxide memristive switches. *Nanotechnology* 20:215201. doi: 10.1088/0957-4484/20/21/215201

- Kim, W., Menzel, S., Wouters, D. J., Guo, Y., Robertson, J., Roesgen, B., et al. (2016). Impact of oxygen exchange reaction at the ohmic interface in Ta 2 O 5 -based ReRAM devices. *Nanoscale* 8, 17774–17781. doi: 10.1039/C6NR03810G

- Kindsmüller, A., Meledin, A., Mayer, J., Waser, R., and Wouters, D. J. (2019).

On the role of the metal oxide/reactive electrode interface during the forming procedure of valence change ReRAM devices. *Nanoscale* 11, 18201–18208. doi: 10.1039/C9NR06624A

- Lamb, D. R., and Rundle, P. C. (1967). A non-filamentary switching action in thermally grown silicon dioxide films. Br. J. Appl. Phys. 18, 29–32. doi: 10.1088/0508-3443/18/1/306

- Lassner, E., and Schubert, W.-D. (1999). Tungsten. Boston, MA: Springer US. doi: 10.1007/978-1-4615-4907-9

- Lee, J. H., Wu, C., Sung, S., An, H., and Kim, T. W. (2019). Highly flexible and stable resistive switching devices based on WS2 nanosheets:poly(methylmethacrylate) nanocomposites. *Sci. Rep.* 9:19316. doi: 10.1038/s41598-019-55637-2

- Lee, M.-J., Kang, B. S., Ahn, S.-E., Kim, K. H., Lee, C. B., Kim, C. J., et al. (2009). Electrical manipulation of nanofilaments in transition-metal oxides for resistance-based memory. *Nano Lett.* 9, 1476–1481. doi: 10.1021/nl803387q

- Lin, Y. S., Zeng, F., Tang, S. G., Liu, H. Y., Chen, C., Gao, S., et al. (2013). Resistive switching mechanisms relating to oxygen vacancies migration in both interfaces in Ti/HfOx/Pt memory devices. *J. Appl. Phys.* 113:064510. doi: 10.1063/1.4791695

- Marconi, G. (1899). Wireless telegraphy. J. Inst. Electr. Eng. 28, 273–290. doi: 10.1049/jiee-1.1899.0010

- Meena, J. S., Sze, S. M., Chand, U., and Tseng, T. Y. (2014). Overview of emerging nonvolatile memory technologies. *Nanoscale Res. Lett.* 9:526. doi: 10.1186/1556-276X-9-526

- Nafria, M., Rodriguez, R., Porti, M., Martin-Martinez, J., Crespo-Yepes, A., Claramunt, S., et al. (2017). (Invited) advanced measurement techniques for the characterization of ReRAM devices. ECS Trans. 79, 139–148. doi:10.1149/07901.0139ecst

- Rahaman, S. Z., Lin, Y.-D., Lee, H.-Y., Chen, Y.-S., Chen, P.-S., Chen, W.-S., et al. (2017). The role of Ti buffer layer thickness on the resistive switching properties of hafnium oxide-based resistive switching memories. *Langmuir* 33, 4654–4665. doi: 10.1021/acs.langmuir.7b 00479

- Shahrabi, E., Giovinazzo, C., Hadad, M., LaGrange, T., Ramos, M., Ricciardi, C., et al. (2019). Switching kinetics control of W-based ReRAM cells in transient operation by interface engineering. Adv Electron Mater. 5:1800835. doi: 10.1002/aelm.201800835

- Singh, A. K., Blonkowski, S., and Kogelschatz, M. (2018). Resistive switching study in HfO2 based resistive memories by conductive atomic force microscopy in vacuum. J. Appl. Phys. 124, 014501. doi: 10.1063/1.50 25143

- Sun, Y. M., Song, C., Yin, J., Qiao, L. L., Wang, R., Wang, Z. Y., et al. (2019). Modulating metallic conductive filaments via bilayer oxides in resistive switching memory. Appl. Phys. Lett. 114:193502. doi: 10.1063/1.50 98382

- Tang, J., Yuan, F., Shen, X., Wang, Z., Rao, M., He, Y., et al. (2019). Bridging biological and artificial neural networks with emerging neuromorphic devices: fundamentals, progress, and challenges. Adv. Mater. 31:1902761. doi: 10.1002/adma.201902761

- Tappertzhofen, S., Waser, R., and Valov, I. (2014). Impact of the counter-electrode material on redox processes in resistive switching memories. *ChemElectroChem* 1, 1287–1292. doi: 10.1002/celc.201402106

- Tirano, S., Perniola, L., Buckley, J., Cluzel, J., Jousseaume, V., Muller, C., et al. (2011). Accurate analysis of parasitic current overshoot during forming operation in RRAMs. *Microelectron. Eng.* 88, 1129–1132. doi:10.1016/j.mee.2011.03.062

- Valov, I. (2014). Redox-based resistive switching memories (ReRAMs): Electrochemical systems at the atomic scale. ChemElectroChem 1, 26–36. doi:10.1002/celc.201300165

- Valov, I., Waser, R., Jameson, J. R., and Kozicki, M. N. (2011). Electrochemical metallization memories—fundamentals, applications, prospects. Nanotechnology 22:254003. doi: 10.1088/0957-4484/22/28/289502

- Walczyk, D., Bertaud, T., Sowinska, M., Lukosius, M., Schubert, M. A., Fox, A., et al. (2012). "Resistive switching behavior in TiN/HfO2/Ti/TiN devices," in 2012 International Semiconductor Conference Dresden-Grenoble (ISCDG) (Grenoble: IEEE), 143–146. doi: 10.1109/ISCDG.2012.6360035

- Wang, Z., Wu, H., Burr, G. W., Hwang, C. S., Wang, K. L., Xia, Q., et al. (2020). Resistive switching materials for information processing. *Nat. Rev. Mater.* 5, 173–195. doi: 10.1038/s41578-019-0159-3

- Waser, R., and Aono, M. (2007). Nanoionics-based resistive switching memories. Nat. Mater. 6, 833–840. doi: 10.1038/nmat2023

- Wong, H. S. P., Lee, H. Y., Yu, S., Chen, Y. S., Wu, Y., Chen, P. S., et al. (2012). Metal-oxide RRAM. Proc. IEEE 100, 1951–1970. doi: 10.1109/IPROC.2012.2190369

- Xia, Q., and Yang, J. J. (2019). Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323. doi: 10.1038/s41563-019-0291-x

- Yang, J. J., Zhang, M. X., Strachan, J. P., Miao, F., Pickett, M. D., Kelley, R. D., et al. (2010). High switching endurance in TaOx memristive devices. *Appl. Phys. Lett.* 97, 6–9. doi: 10.1063/1.3524521

- Yen, T. J., Gismatulin, A., Volodin, V., Gritsenko, V., and Chin, A. (2019). All nonmetal resistive random access memory. Sci. Rep 9:6144. doi: 10.1038/s41598-019-42706-9

- Zidan, M. A., Jeong, Y. J., Lee, J., Chen, B., Huang, S., Kushner, M. J., et al. (2018).

A general memristor-based partial differential equation solver. *Nat Electron* 1, 411–420. doi: 10.1038/s41928-018-0100-6

**Conflict of Interest:** The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Copyright © 2020 Fra, Shahrabi, Leblebici and Ricciardi. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms

## Advances in Memristor-Based Neural Networks

Weilin Xu 1,2,3\*†, Jingjuan Wang 1† and Xiaobing Yan 1,4\*

<sup>1</sup> Key Laboratory of Brain-Like Neuromorphic Devices and Systems of Hebei Province, College of Electron and Information Engineering, Hebei University, Baoding, China, <sup>2</sup> Guangxi Key Laboratory of Precision Navigation Technology and Application, Guilin University of Electronic Technology, Guilin, China, <sup>3</sup> Electrical and Computer Engineering Department, Southern Illinois University Carbondale, Carbondale, IL, United States, <sup>4</sup> Department of Materials Science and Engineering, National University of Singapore, Singapore

The rapid development of artificial intelligence (AI), big data analytics, cloud computing, and Internet of Things applications expect the emerging memristor devices and their hardware systems to solve massive data calculation with low power consumption and small chip area. This paper provides an overview of memristor device characteristics, models, synapse circuits, and neural network applications, especially for artificial neural networks and spiking neural networks. It also provides research summaries, comparisons, limitations, challenges, and future work opportunities.

Keywords: memristor, integrated circuit, artificial neural network, spiking neural network, artificial intelligence

#### **OPEN ACCESS**

#### Edited by:

J. Joshua Yang, University of Southern California, United States

#### Reviewed by:

Rivu Midya, University of Massachusetts Amherst, United States Zhongrui Wang, The University of Hong Kong, Hong Kong

#### \*Correspondence:

Weilin Xu xwl@guet.edu.cn Xiaobing Yan xiaobing\_yan@126.com

<sup>†</sup>These authors have contributed equally to this work

#### Specialty section:

This article was submitted to Nanodevices, a section of the journal Frontiers in Nanotechnology

Received: 24 December 2020 Accepted: 03 March 2021 Published: 24 March 2021

#### Citation

Xu W, Wang J and Yan X (2021) Advances in Memristor-Based Neural Networks. Front. Nanotechnol. 3:645995.

doi: 10.3389/fnano.2021.645995

#### INTRODUCTION

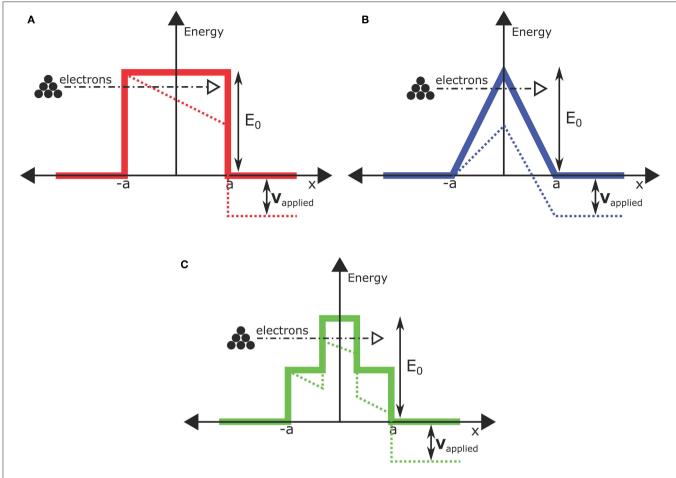

Resistance, capacitance and inductance are the three basic circuit components in passive circuit theory. In 1971, Professor Leon O. Chua of the University of California at Berkeley first described a basic circuit that relates flux to charge, called the missing fourth memristor element, and was successfully found by a team led by Stanley Williams at HP Labs in 2008 (Chua, 1971; Strukov et al., 2008). As a non-linear two-terminal passive electrical component, studies have shown that the conductance of a memristor is tunable by adjusting the amplitude, direction, or duration of its terminal voltages. Memristors have shown various outstanding properties, such as good compatibility with CMOS technology, small device area for high-density on-chip integration, non-volatility, fast speed, low power dissipation, and high scalability (Lee et al., 2008; Waser et al., 2009; Akinaga and Shima, 2010; Wong et al., 2012; Yang et al., 2013; Choi et al., 2014; Sun et al., 2020; Wang et al., 2020; Zhang et al., 2020). Thus, although memristors took many years to transform from a purely theoretical derivation into a feasible implementation, these devices have been widely used in applications such as machine learning and neuromorphic computing, as well as non-volatile random-access memory (Alibart et al., 2013; Liu et al., 2013; Sarwar et al., 2013; Fackenthal et al., 2014; Prezioso et al., 2015; Midya et al., 2017; Yan et al., 2017, 2019b,d; Ambrogio et al., 2018; Krestinskaya et al., 2018; Li C. et al., 2018, Li et al., 2019; Wang et al., 2018a, 2019a,b; Upadhyay et al., 2020). Furthermore, thanks to its powerful computing and storage capability, a memristor is a promising device for processing tremendous data and increasing the data processing efficiency in neural networks for artificial intelligence (AI) applications (Jeong and Shi, 2018).

This article intends to analyze the memristor theory, models, circuits, and important applications in neural networks. The contents of this paper are organized as follows. Section Memristor Characteristics and Models introduces the memristor theory and models. Section Memristor-Based Neural Networks presents its applications in the second-generation neural networks, namely artificial neural networks (ANNs) and the third-generation neural networks, namely spiking neural networks (SNNs). Section Summary is the conclusions and future research direction.

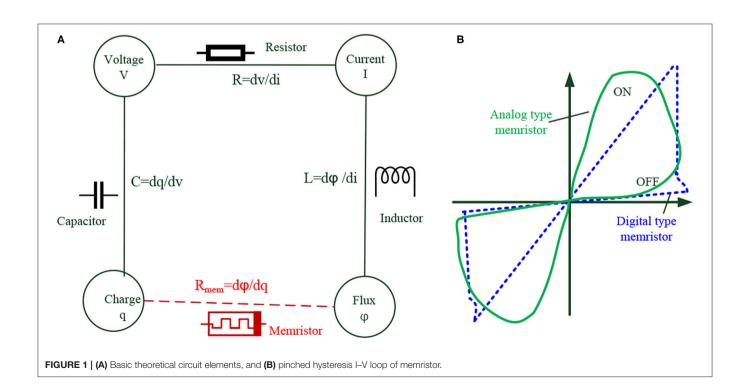

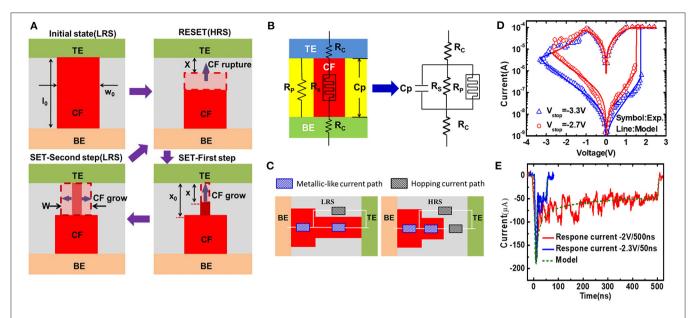

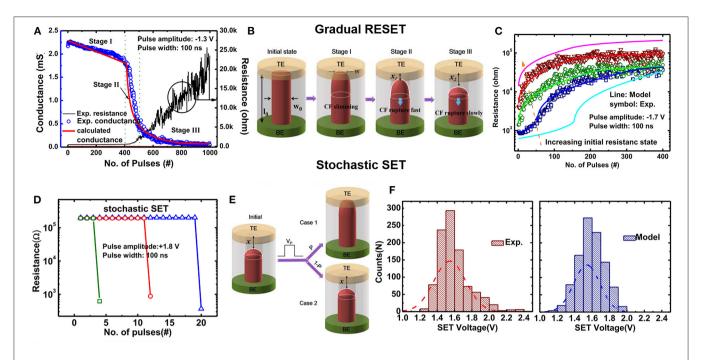

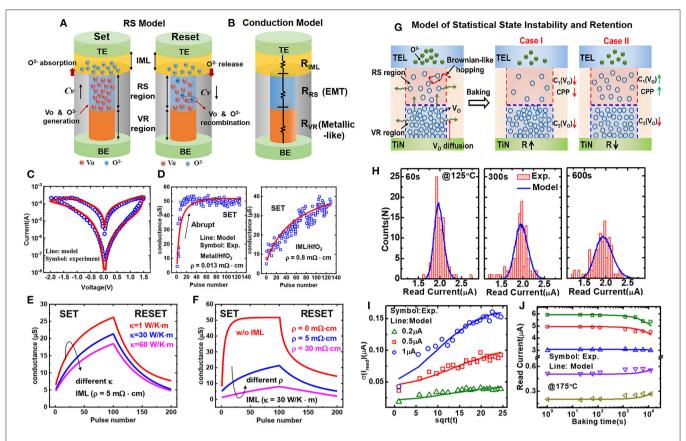

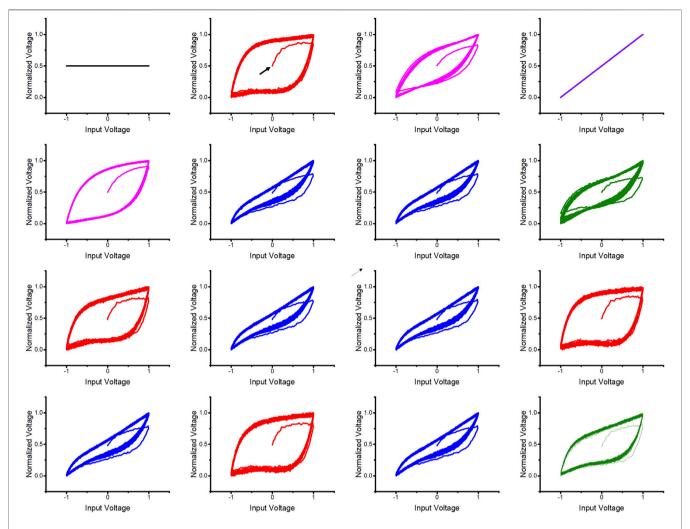

## MEMRISTOR CHARACTERISTICS AND MODELS

The relationship between the physical quantities (namely charge q, voltage v, flux  $\varphi$ , and current i) and basic circuit elements (namely resistor R, capacitor C, inductor L, and memristor M) is shown in Figure 1A (Chua, 1971). Specifically, C defined as a linear relationship between voltage v and electric charge q (C = dq/dv), L is defined as a relationship between magnetic flux  $\varphi$ and current i ( $L = d\varphi/di$ ), R is defined as a relationship between voltage v and current i (R = dv/di). The missing link between the electric charge and flux is defined as the memristor M and its differential equation is  $M = d\varphi/dq$  or  $G = dq/d\varphi$ . Figure 1B shows the current-voltage characteristics of the memristor, where the pinched hysteresis loop is its fundamental identifier (Yan et al., 2018c). As a basic element, the memristor I-V curve cannot be obtained using R, C, and L. According to the shape of the pinched curve, it can be roughly classified into a digital type memristor or an analog type memristor. The resistance of a digital memristor exhibits an abrupt change at higher resistance ratios. The high-resistance and low-resistance states in a digital memristor have a long retention period, making it ideal for memory and logic operations. An analog memristor exhibits a gradual change in resistance. Therefore, it is more suitable for analog circuits and hardware-based multi-state neuromorphic system applications.

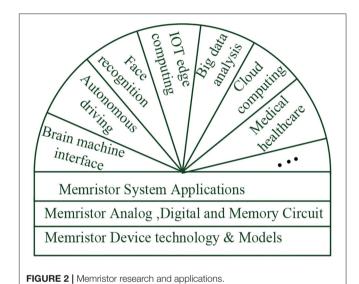

Memristor device technology and modeling research are the cornerstones of system applications. As shown in Figure 2, top-level system applications (brain-machine interface, face or picture recognition, autonomous driving, IoT edge computing, big data analytics, and cloud computing) are built on the device

technology and modeling. Memristor-based analog, digital, and memory circuits play a key role in the link between device materials and system applications. The main usage for bistable memristors is binary switches, binary memory, and digital logic circuits, while multi-state memristors are used as multi-bit memories, reconfigurable analog circuits, and neuromorphic circuits.

Since the HP labs verified the nanoscale physical implementation, the physical behavior models of memristors have received a lot of attention. Accuracy, convergence, and

TABLE 1 | Classic memristor models.

| Models                            | Linear ion drift                                                                           | Non-linear ion<br>drift                                                                | Simmons tunnel barrier                                                                                                                                                                                                                                                                                       | TEAM                                                                                                                                                                            |

|-----------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I–V characteristic                | $ v(t) = \left( Ron \frac{w(t)}{D} + Roff \left( 1 - \frac{w(t)}{D} \right) \right) i(t) $ | $i(t) = w(t)^{n} \beta \sinh(\alpha v(t)) + \chi \left[ \exp(\gamma v(t)) - 1 \right]$ | $v(t) = \left(Ron + \frac{Roff - Ron}{Woff - Won} (w - won)\right) i(t)$                                                                                                                                                                                                                                     | $V(t) = R_{on} \cdot \frac{\lambda}{e^{wolf-won}} (W - won)$                                                                                                                    |

| State variable $\frac{dw(t)}{dt}$ | $\left(u_{V}\frac{R_{On}}{D}\right)i(t)$                                                   | a-f (w) <b>v(t)</b> <sup>m</sup>                                                       | $ \begin{cases} coff - \sinh\left(\frac{i}{ioff}\right) \exp\left[-\exp\left(\frac{w-aoff}{wc} - \frac{ i }{b}\right) - \frac{w}{wc}\right], \\ i > 0 \\ coff - \sinh\left(\frac{i}{ioff}\right) \exp\left[-\exp\left(\frac{w-aoff}{wc} - \frac{ i }{b}\right) - \frac{w}{wc}\right], \\ i < 0 \end{cases} $ | $\begin{cases} koff \left(\frac{i(t)}{ioff} - 1\right)^{aoff}, \ 0 < ioff < i \\ kon\left(\frac{i(t)}{ion} - 1\right)^{aon}, \ 0 < ioff < i \\ 0, \qquad otherwise \end{cases}$ |

| Interval                          | $0 \le w \le D$                                                                            | $0 \le w \le 1$                                                                        | $aoff \le w \le aon$                                                                                                                                                                                                                                                                                         | $aon \le w \le aoff$                                                                                                                                                            |

| Control                           | Current                                                                                    | Voltage-controlled                                                                     | Current-controlled                                                                                                                                                                                                                                                                                           | Current-controlled                                                                                                                                                              |

| mechanism                         | controlled                                                                                 |                                                                                        |                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                 |

| Accuracy                          | Lowest accuracy                                                                            | Low accuracy                                                                           | Highest accuracy                                                                                                                                                                                                                                                                                             | Sufficient accuracy                                                                                                                                                             |

| Thershold exists                  | No                                                                                         | No                                                                                     | Pracitcally exists                                                                                                                                                                                                                                                                                           | Yes                                                                                                                                                                             |

| Linearity                         | linear                                                                                     | No-linear                                                                              | No-linear                                                                                                                                                                                                                                                                                                    | No-linear                                                                                                                                                                       |

computational efficiency are the most important factors in memristor models. These behavior models are expected to be simple, intuitive, better understood, and closed form. Up to date, various models have been developed, each with its unique advantages and shortcomings. The models listed in Table 1 are the most popular models, including a linear ion drift memristor model, a non-linear ion drift memristor model, a Simmons tunnel barrier memristor model, a threshold adaptive memristor model (TEAM) (Simmons, 1963; Strukov et al., 2008; Biolek et al., 2009; Pickett et al., 2009; Kvatinsky et al., 2012). In the linear ion drift memristor model, D and  $u_v$  represent the full length and device mobility of a memristor film, respectively.  $\omega(t)$ is a dynamic state variable whose value is limited between 0 and D, taking into account the size of the physical device. The low turn-on resistance  $R_{on}$  is the full doped resistance when dynamic variable  $\omega(t)$  is equal to D. The high turn-off resistance  $R_{off}$ is a fully undoped resistance when  $\omega(t)$  is equal to 0. Besides, a window function multiplied by a state variable is needed to nullify the derivative and provide a non-linear transition for the physical boundary simulation. Several window functions have been presented for modeling memristors such as Biolek, Strukov, Joglekar, and Prodromakis window functions (Strukov et al., 2008; Biolek et al., 2009; Joglekar and Wolf, 2009; Strukov and Williams, 2009; Prodromakis et al., 2011). As the first memristor model, the linear ion drift model shows the features of simple, intuitive, and better understood. However, the state variable  $\omega$  modulation in nano-scale devices is not a linear process, and the memristor experimental results show non-linear I-V characteristics. The non-linear ion drift model provides a better description of non-linear ionic transport and higher accuracy by experimentally fitting the parameters n,  $\beta$ ,  $\alpha$ , and  $\chi$  (Biolek et al., 2009). But more physical reaction kinetics still need to be considered. The Simmons tunnel barrier model consists of a resistor in series with an electron tunnel barrier, which provides a more detailed representation of non-linear and asymmetrical features (Simmons, 1963; Pickett et al., 2009). There are nine fitting parameters in this segmentation model, which makes

the mathematical model very complicated and computationally inefficient. The TEAM model can be thought of as a simplified version of the Simmons tunnel barrier model (Kvatinsky et al., 2012). However, all of the above models suffer from smoothing problems or mathematical ill-posedness issues, and they cannot provide robust and predictable simulation results in DC, AC, transient analysis, not to mention complicated circuit analysis such as noise analysis and periodic steady-state analysis (Wang and Roychowdhury, 2016). Therefore, in the face of transistorlevel circuit design simulation, circuit designers usually have to replace the actual memristor with an emulator (Yang et al., 2019). The emulator is a complex CMOS circuit used to simulate some performance aspect of a special memristor. An emulator is not a true model, and it is very different from the real memristor model (Yang et al., 2014). Thus, it is urgent to establish a complete memristor model. Correct bias definition and right physical characteristics in SPICE or Verilog-a model are important for complex memristor circuit design. Otherwise, non-physical predictions will confuse circuit engineers in physical chip design.

#### MEMRISTOR-BASED NEURAL NETWORKS

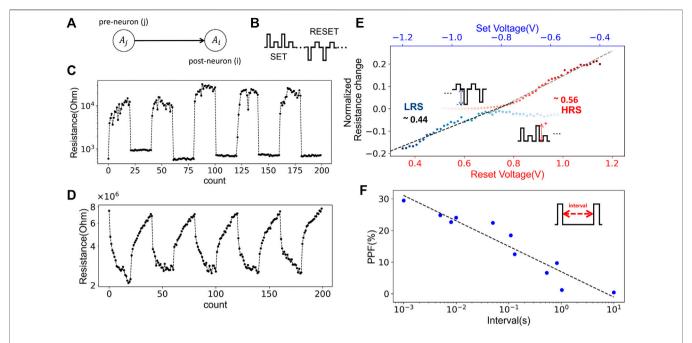

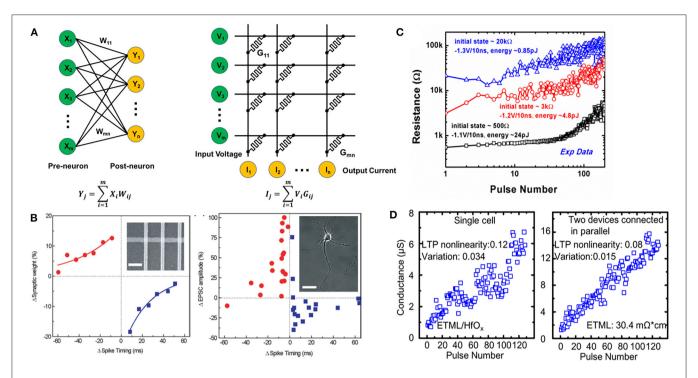

## Neuron Biological Mechanisms and Memristive Synapse

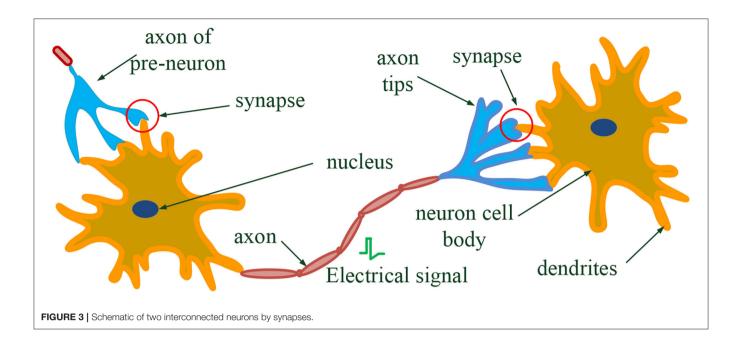

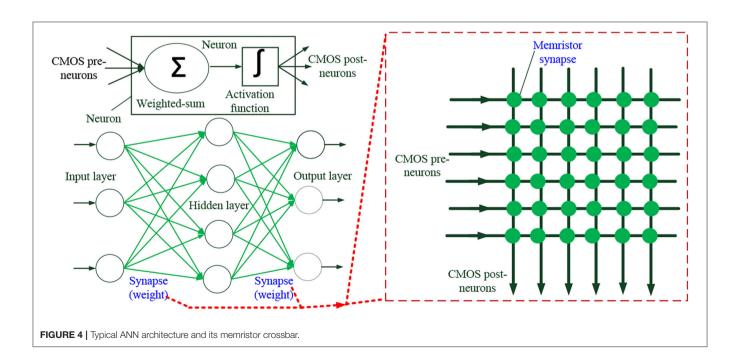

The human brain can solve complex tasks, such as image recognition and data classification, more efficiently than traditional computers. The reason why a brain excels in complicated functions is the large number of neurons and synapses that process information in parallel. As shown in **Figure 3**, when an electrical signal is transmitted between two neurons via axon and synapse, the joint strength or weight is adjusted by the synapse. There are approximately 100 billion neurons in an entire human brain, each with about 10,000 synapses. Pre-synaptic and post-synaptic neurons transfer and receive the signal of excitatory and inhibitory

post-synaptic potentials by updating synaptic weights. Long-term potentiation (LTP) and long-term depression (LTD) are important mechanisms in a biological nervous system, which indicates a deep-rooted transformation in the connection strengths between neurons. According to the interval between pre-synaptic and post-synaptic action potentials or spikes, the phenomenon of synaptic weight modification is known as spike-timing-dependent plasticity (STDP) (Yan et al., 2018a, 2019c). Due to scalability, low power operation, non-volatile features, and small on-chip area, memristors are good candidates for artificial synaptic devices to mimicking the LTP, LTD, and STDP behaviors (Jo et al., 2010; Ohno et al., 2011; Kim et al., 2015; Wang et al., 2017; Yan et al., 2017).

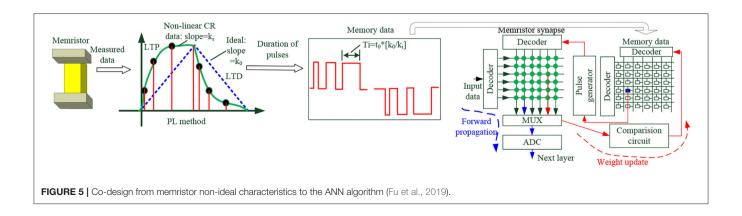

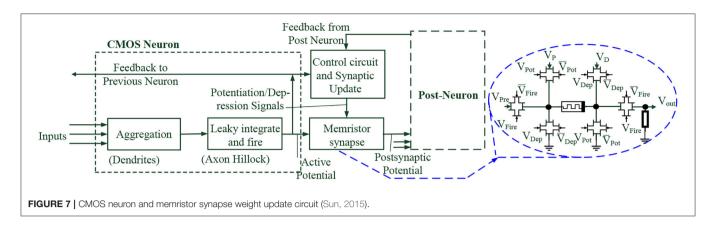

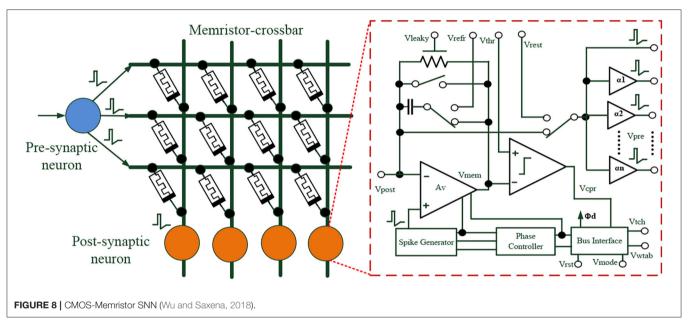

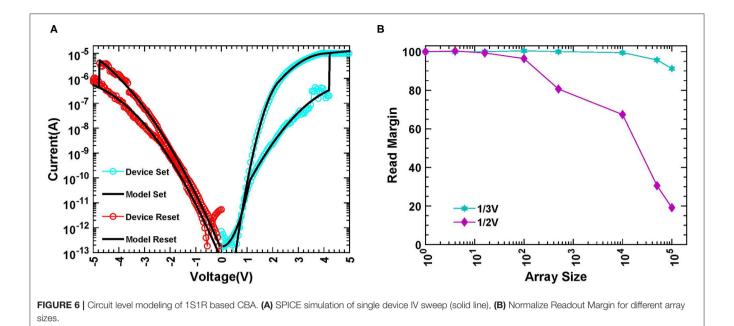

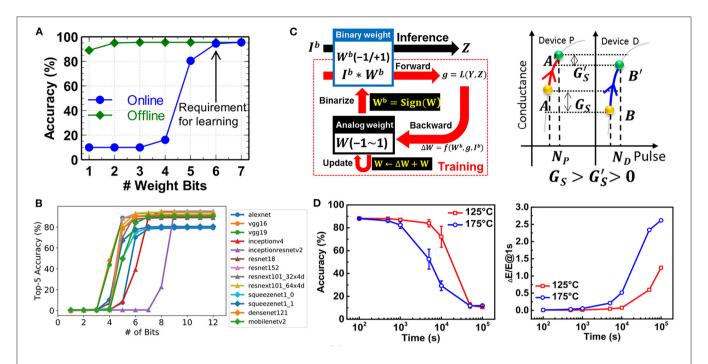

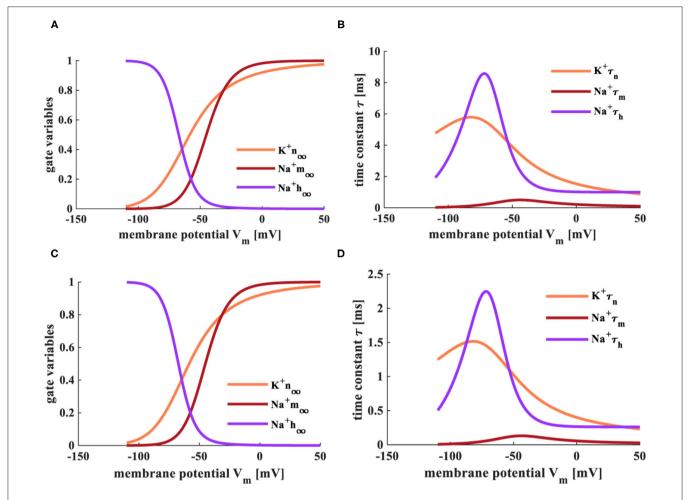

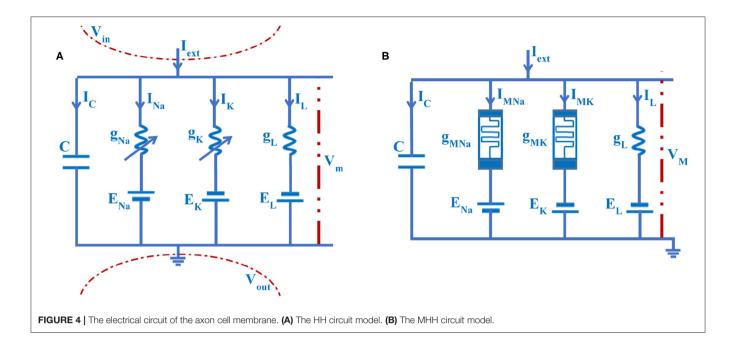

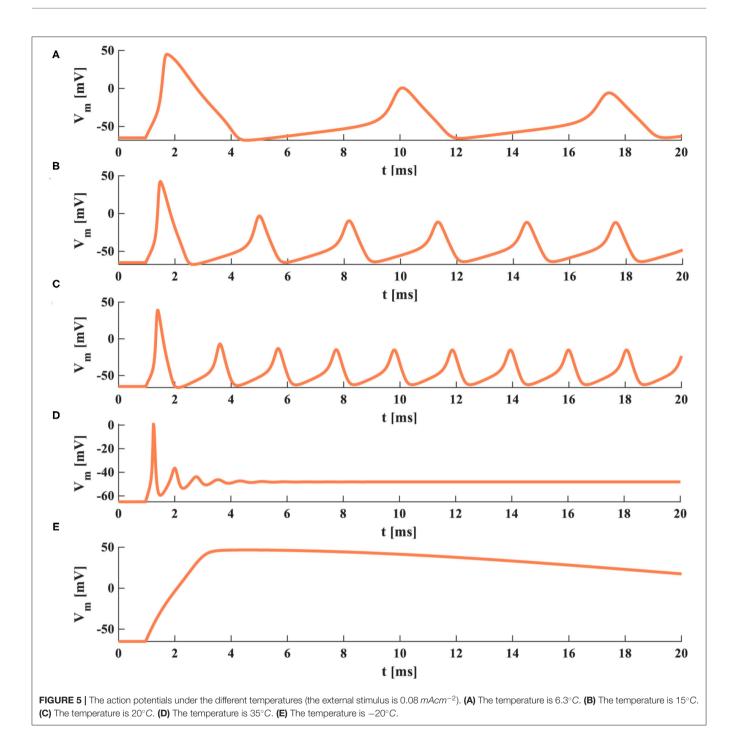

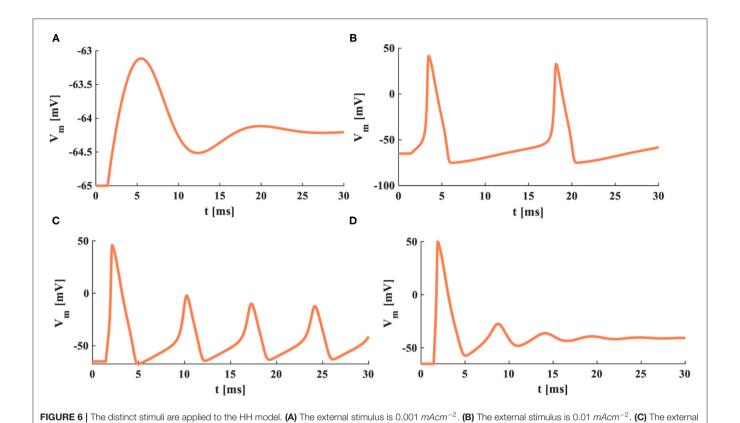

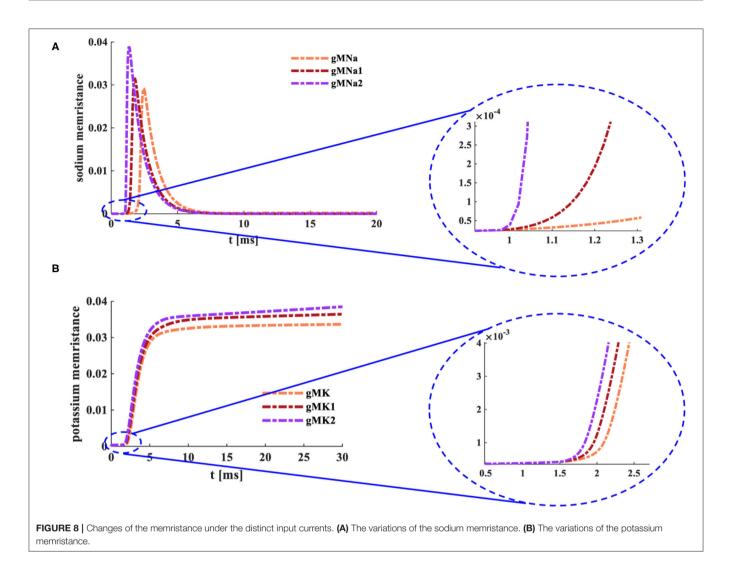

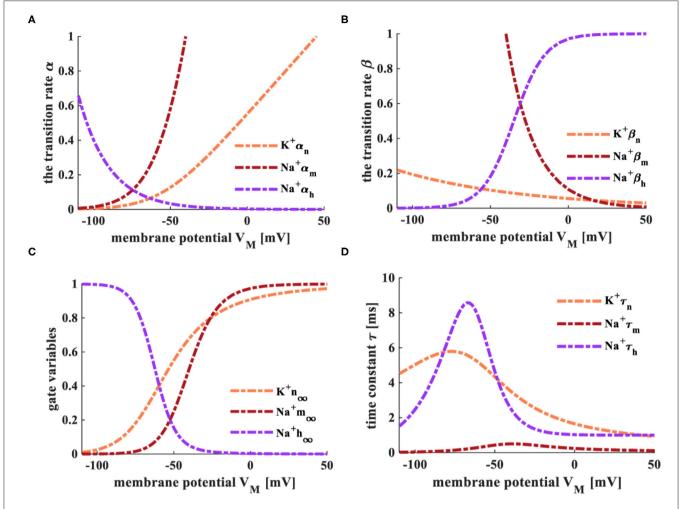

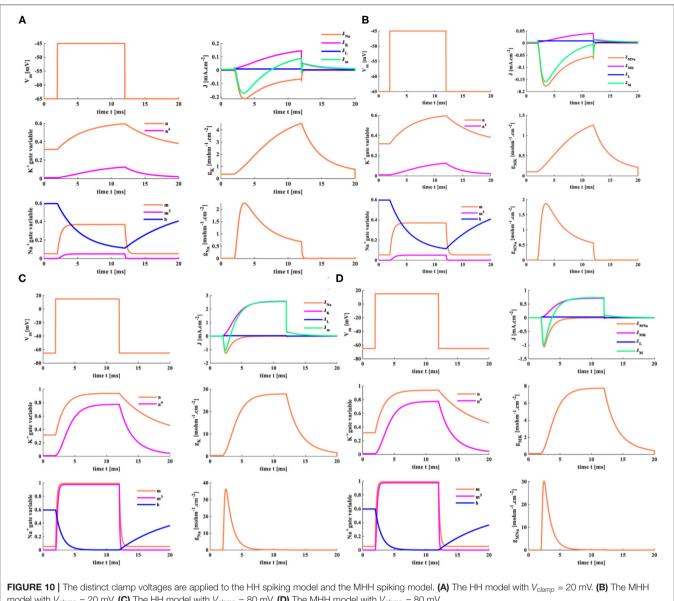

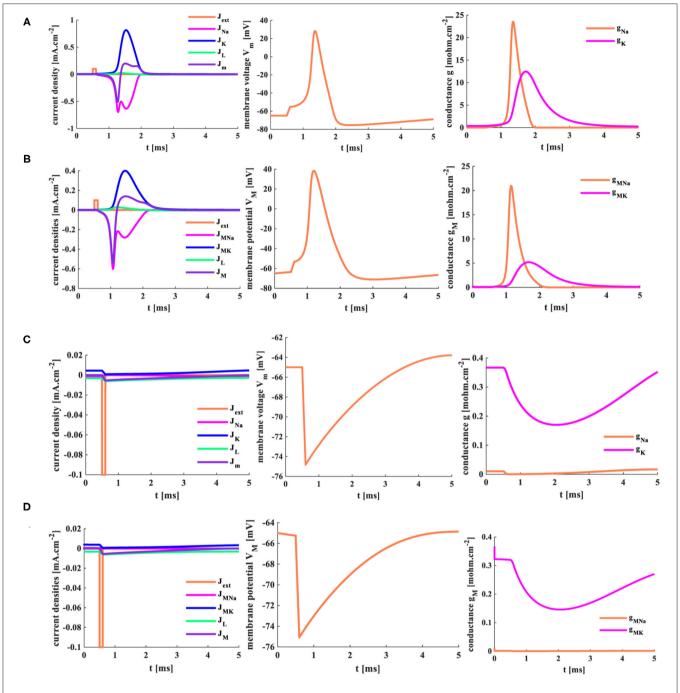

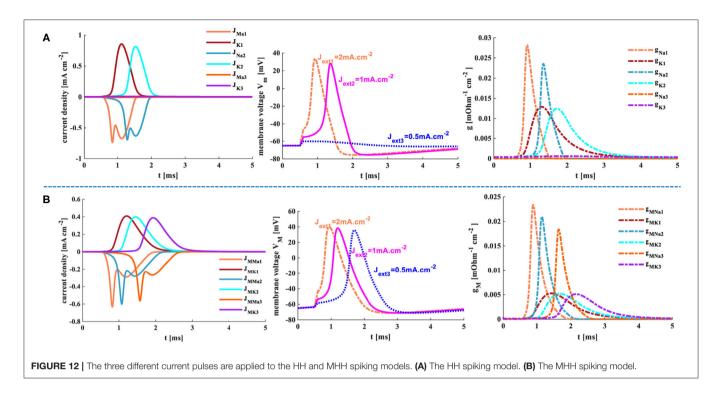

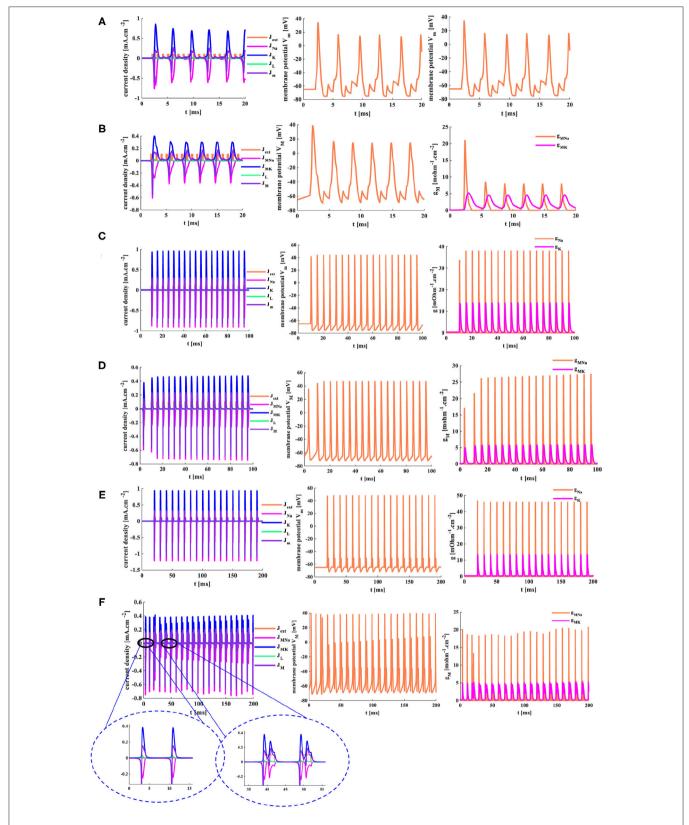

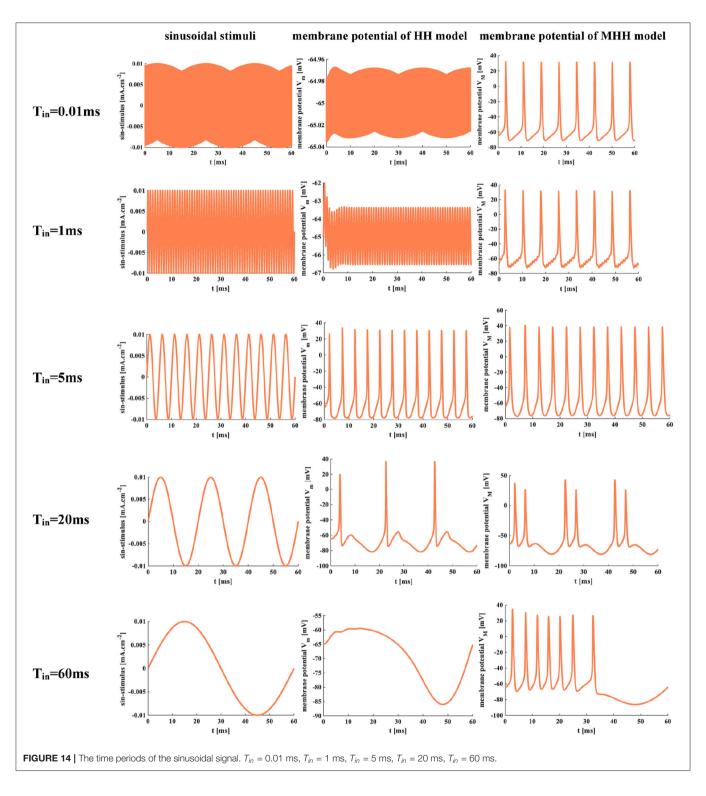

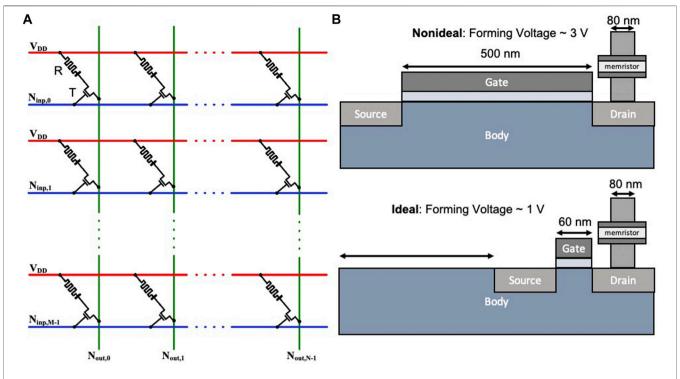

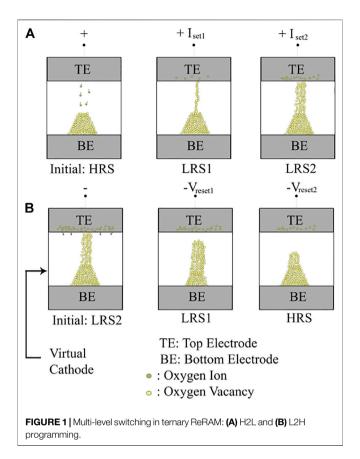

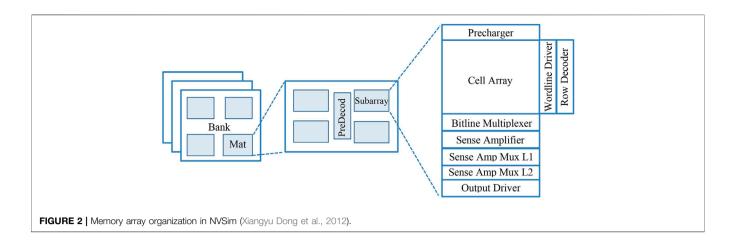

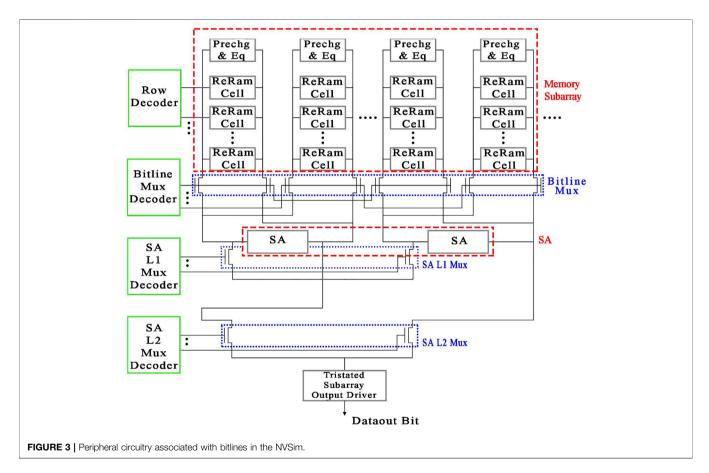

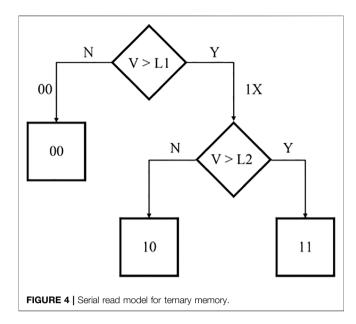

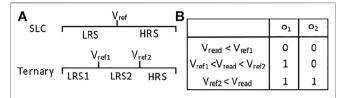

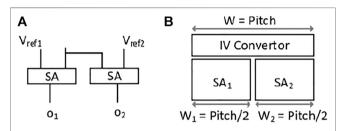

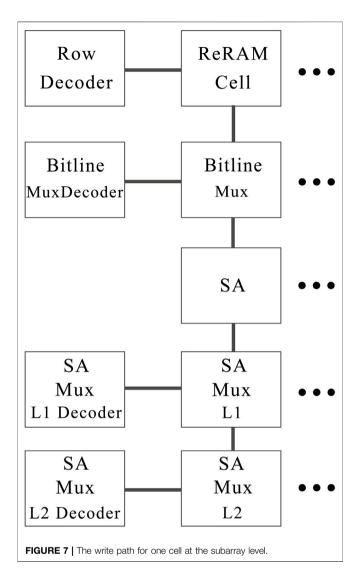

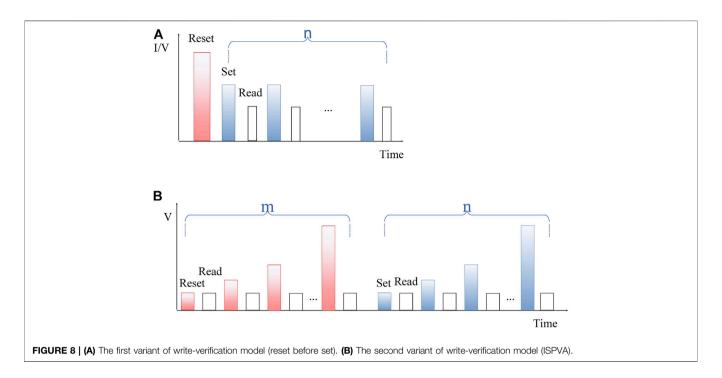

There are some key requirements for memristive devices in neural network applications. For example, a wide range of resistance is required to enable sufficient resistance states; devices are required to have low resistance fluctuations and low deviceto-device variability; a higher absolute resistance is required for low power dissipation; and high durability is required for reprogramming and training (Choi et al., 2018; Yan et al., 2018b, 2019a; Xia and Yang, 2019). A concern with device stability is resistance drift, which occurs over time or with the environment. Resistance drift causes undesirable changes in synapse weight and blurs different resistance states, ultimately affecting the accuracy of neural network computation (Xia and Yang, 2019). To deal with this drift challenge, improvements can be made in three aspects: (1) material device engineering, (2) circuit design, and (3) system design (Alibart et al., 2012; Choi et al., 2018; Jiang et al., 2018; Lastras-Montaño and Cheng, 2018; Yan et al., 2018b, 2019a; Zhao et al., 2020). For example, as for the domain of material engineering, threading dislocations can be used to control programming variation and enhance switching uniformity (Choi et al., 2018). In terms of circuit-level design, a module of two series memristors and a transistor with the smallest size can be used, thus, the resistance ratio of the memristor can be encoded to compensate for the resistance drift (Lastras-Montaño and Cheng, 2018). For the system-design level, device deviation can be reduced by protocols, such as closed loop peripheral circuit with a write-verify function (Alibart et al., 2012). In order to obtain linear and symmetric weight update in LTP and LTD for efficient neural network training, optimized programming pulses can be used to excite memristors with either fixed-amplitude or fixed-width voltage pulses (Jiang et al., 2018; Zhao et al., 2020). Note it is inevitable to increase energy consumption if the memristor resistance value is changed through complex programmable pulses.