# Coordination and control of power converters in modern power systems

#### **Edited by**

Hao Tian, Tao Xu, Pengfeng Lin and Jingyang Fang

#### Published in

Frontiers in Energy Research

#### FRONTIERS EBOOK COPYRIGHT STATEMENT

The copyright in the text of individual articles in this ebook is the property of their respective authors or their respective institutions or funders. The copyright in graphics and images within each article may be subject to copyright of other parties. In both cases this is subject to a license granted to Frontiers.

The compilation of articles constituting this ebook is the property of Frontiers.

Each article within this ebook, and the ebook itself, are published under the most recent version of the Creative Commons CC-BY licence. The version current at the date of publication of this ebook is CC-BY 4.0. If the CC-BY licence is updated, the licence granted by Frontiers is automatically updated to the new version.

When exercising any right under the CC-BY licence, Frontiers must be attributed as the original publisher of the article or ebook, as applicable.

Authors have the responsibility of ensuring that any graphics or other materials which are the property of others may be included in the CC-BY licence, but this should be checked before relying on the CC-BY licence to reproduce those materials. Any copyright notices relating to those materials must be complied with.

Copyright and source acknowledgement notices may not be removed and must be displayed in any copy, derivative work or partial copy which includes the elements in question.

All copyright, and all rights therein, are protected by national and international copyright laws. The above represents a summary only. For further information please read Frontiers' Conditions for Website Use and Copyright Statement, and the applicable CC-BY licence.

ISSN 1664-8714 ISBN 978-2-8325-4099-2 DOI 10.3389/978-2-8325-4099-2

#### **About Frontiers**

Frontiers is more than just an open access publisher of scholarly articles: it is a pioneering approach to the world of academia, radically improving the way scholarly research is managed. The grand vision of Frontiers is a world where all people have an equal opportunity to seek, share and generate knowledge. Frontiers provides immediate and permanent online open access to all its publications, but this alone is not enough to realize our grand goals.

#### Frontiers journal series

The Frontiers journal series is a multi-tier and interdisciplinary set of open-access, online journals, promising a paradigm shift from the current review, selection and dissemination processes in academic publishing. All Frontiers journals are driven by researchers for researchers; therefore, they constitute a service to the scholarly community. At the same time, the *Frontiers journal series* operates on a revolutionary invention, the tiered publishing system, initially addressing specific communities of scholars, and gradually climbing up to broader public understanding, thus serving the interests of the lay society, too.

#### Dedication to quality

Each Frontiers article is a landmark of the highest quality, thanks to genuinely collaborative interactions between authors and review editors, who include some of the world's best academicians. Research must be certified by peers before entering a stream of knowledge that may eventually reach the public - and shape society; therefore, Frontiers only applies the most rigorous and unbiased reviews. Frontiers revolutionizes research publishing by freely delivering the most outstanding research, evaluated with no bias from both the academic and social point of view. By applying the most advanced information technologies, Frontiers is catapulting scholarly publishing into a new generation.

#### What are Frontiers Research Topics?

Frontiers Research Topics are very popular trademarks of the *Frontiers journals series*: they are collections of at least ten articles, all centered on a particular subject. With their unique mix of varied contributions from Original Research to Review Articles, Frontiers Research Topics unify the most influential researchers, the latest key findings and historical advances in a hot research area.

Find out more on how to host your own Frontiers Research Topic or contribute to one as an author by contacting the Frontiers editorial office: frontiersin.org/about/contact

## Coordination and control of power converters in modern power systems

#### **Topic editors**

Hao Tian — University of Alberta, Canada Tao Xu — Shandong University, China Pengfeng Lin — Nanyang Technological University, Singapore Jingyang Fang — Shandong University, China

#### Citation

Tian, H., Xu, T., Lin, P., Fang, J., eds. (2023). *Coordination and control of power converters in modern power systems*. Lausanne: Frontiers Media SA. doi: 10.3389/978-2-8325-4099-2

## Table of contents

- O4 A switching control method based on a new model considering parasitic capacitance for LLC

- Yetong Han, Dazhong Ma and Qingpeng An

- Optimization strategy and control technology of four-port SOP for distribution network with PV and BESS

- Xingjian Zhao, Xiongying Gao, Xin Zhou and Feng Gao

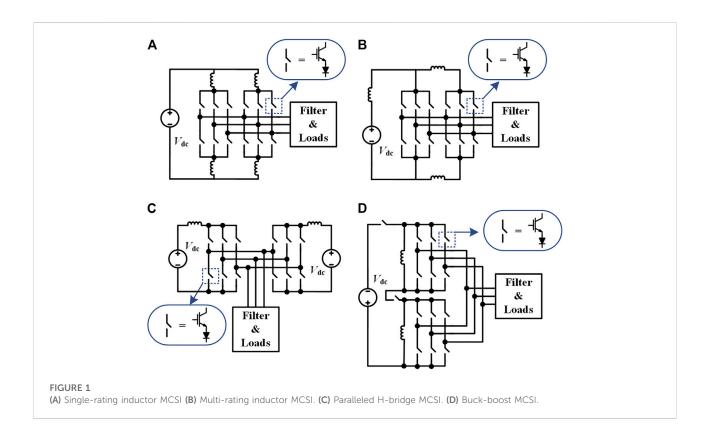

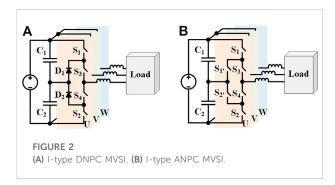

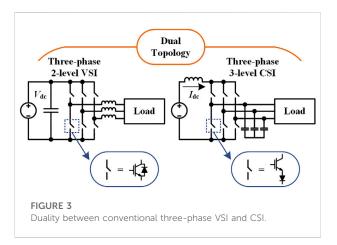

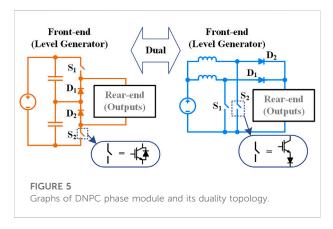

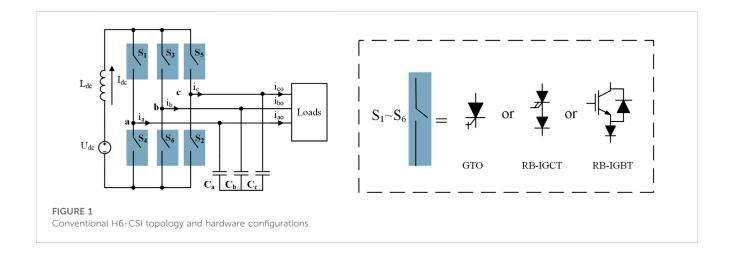

- 28 Three-phase boost-stage coupled current source inverter concept and its space vector modulation

- Weiqi Wang, Xinian Li, Shuling Rui and Xiaoting Xia

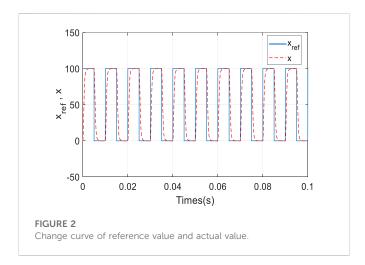

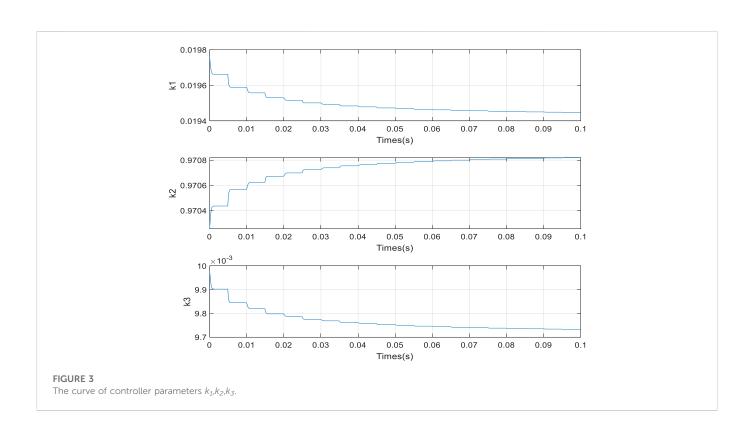

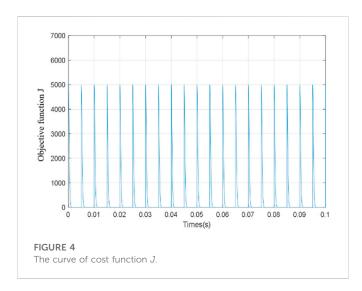

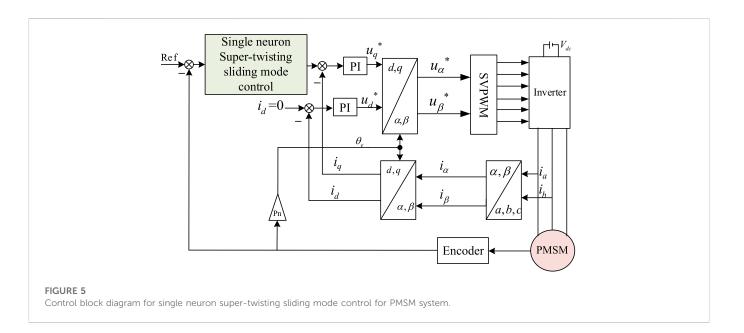

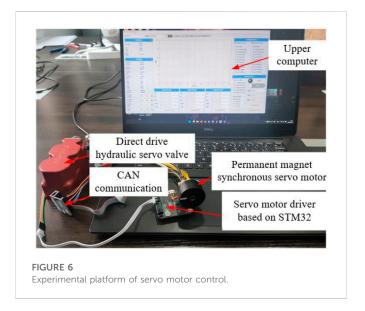

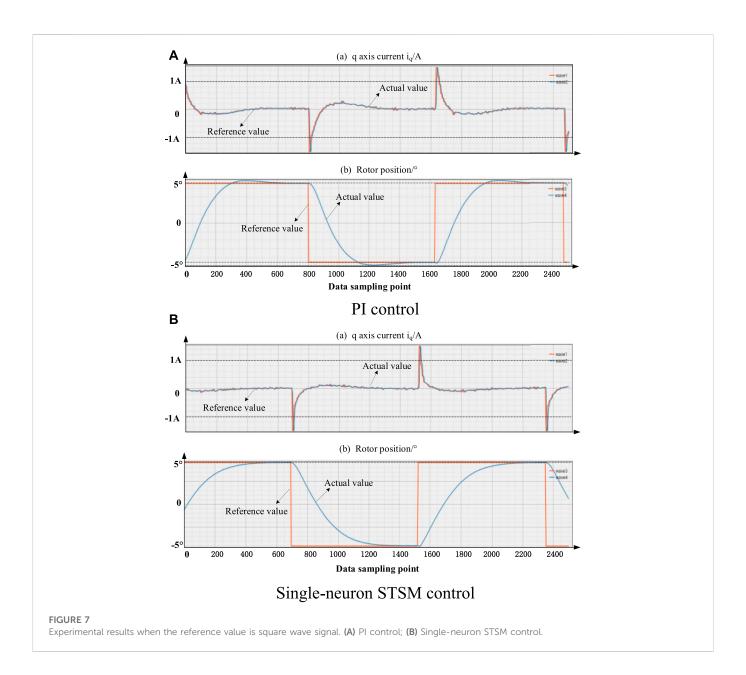

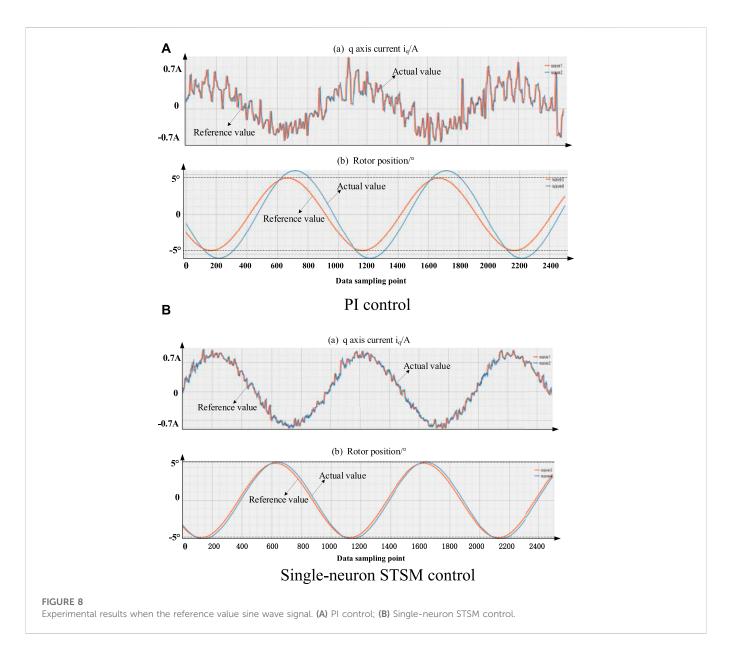

- Design of single neuron super-twisting sliding mode controller for permanent magnet synchronous servo motor Lei Yuan, Hu Chen, Pan Wang, Yi Liu and Anfei Xu

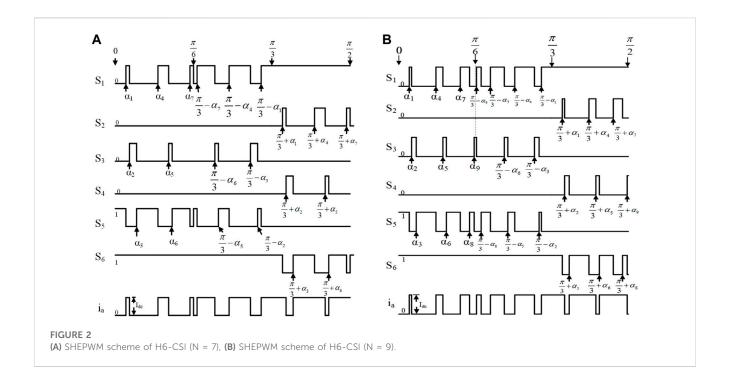

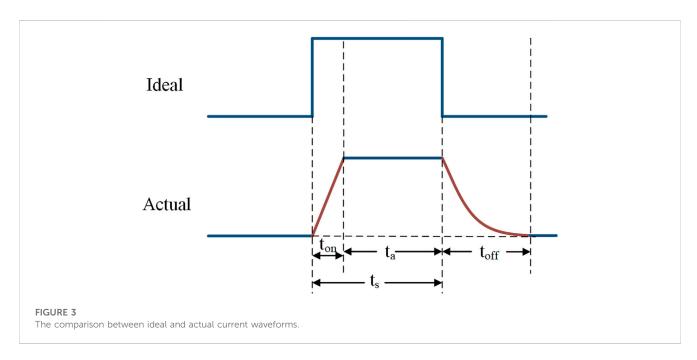

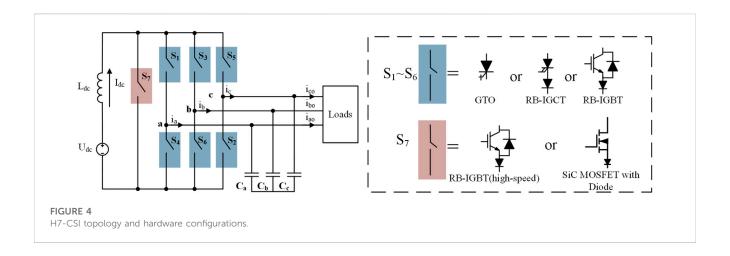

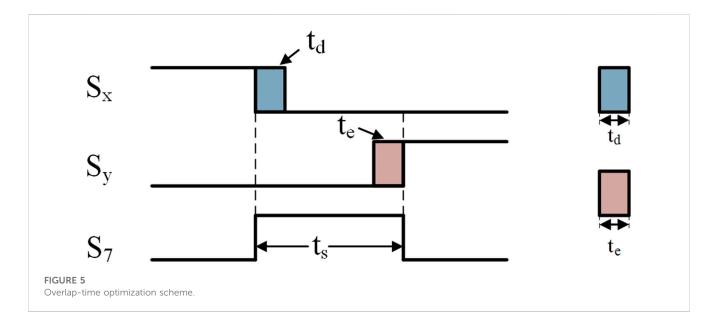

- 47 A strategy for improving the SHEPWM commutation speed of CSI through hybrid switches

- Weiqi Wang, Xiaoting Xia, Shuling Rui, Xiangjian Meng and Yumin Zhang

- A soft start-up method for DC micro-grid based on improved two-level VSC with DC fault ride-through capability

- Weijie Wen, Rui Lyu, Botong Li, Hong Cao, Jiali Yu, Bin Li and Marjan Popov

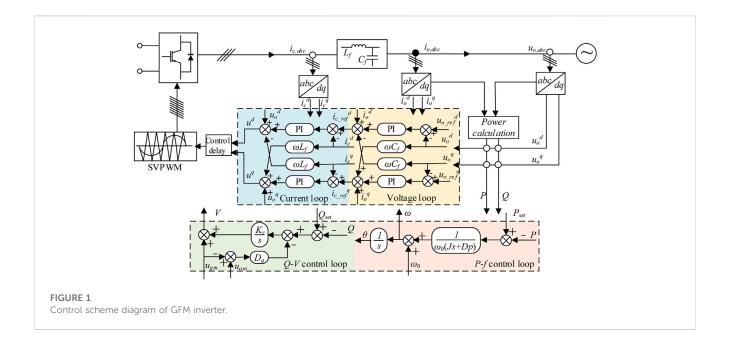

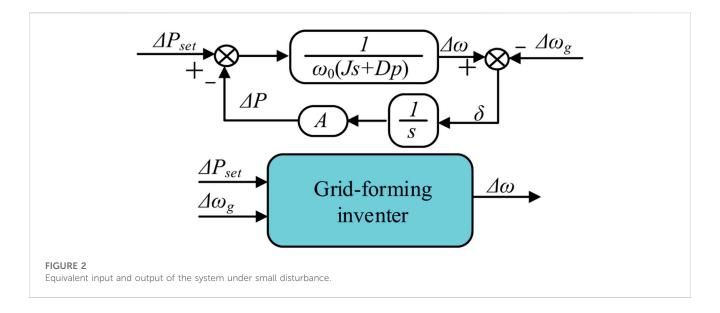

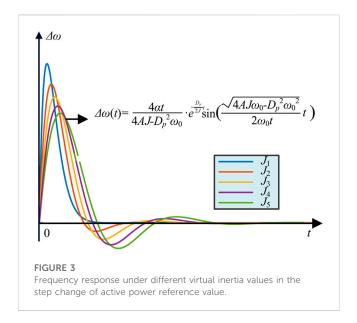

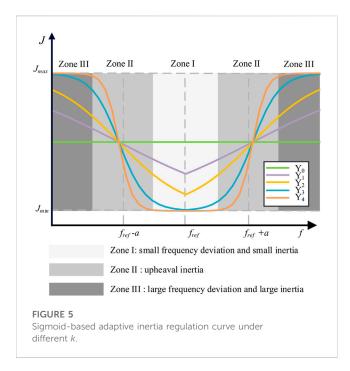

- A sigmoid-based adaptive inertia control strategy for grid-forming inverter to enhance frequency stability

- Renzhi Huang, Chen Dong, Zaijun Wu, Xiangjun Quan, Zichen Wang, Tiankui Sun and Kai Hou

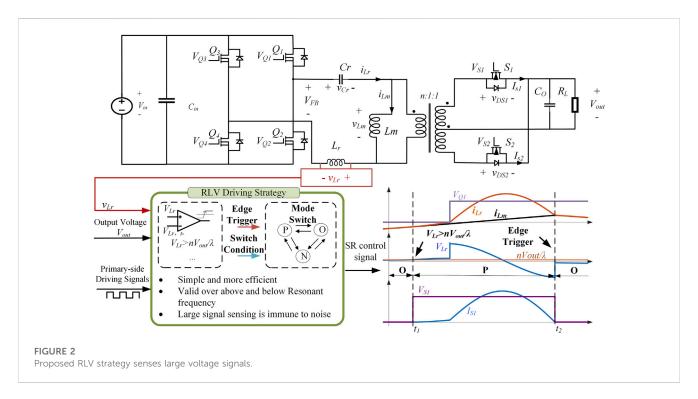

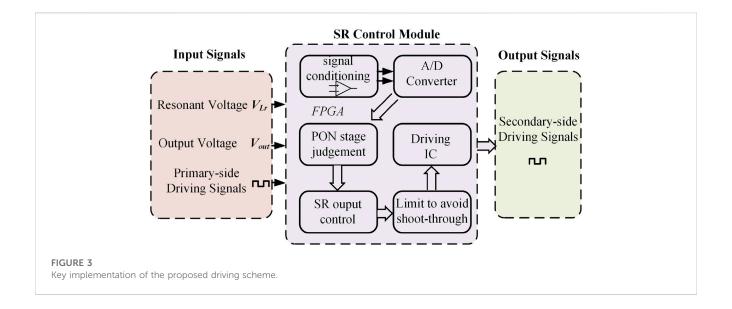

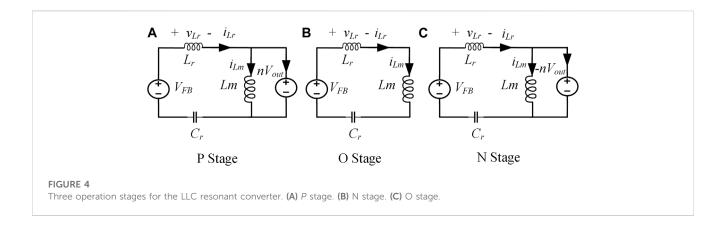

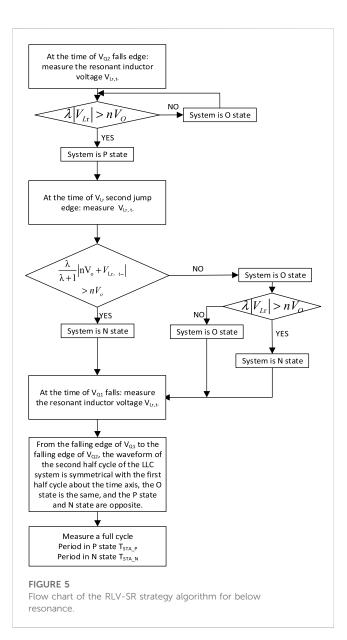

- Synchronous rectification of LLC resonant converters based on resonant inductor voltage

- Zuohao Luo, Zaijun Wu, Xiangjun Quan, Xingfeng Xie, Xiaobo Dou and Qinran Hu

- 92 Current observer-based critical conduction mode control of a bidirectional DC–DC converter in battery charging/discharging applications

- Dai Wan, Jinliang Li, Lulin Zhang and Jingtao Xu

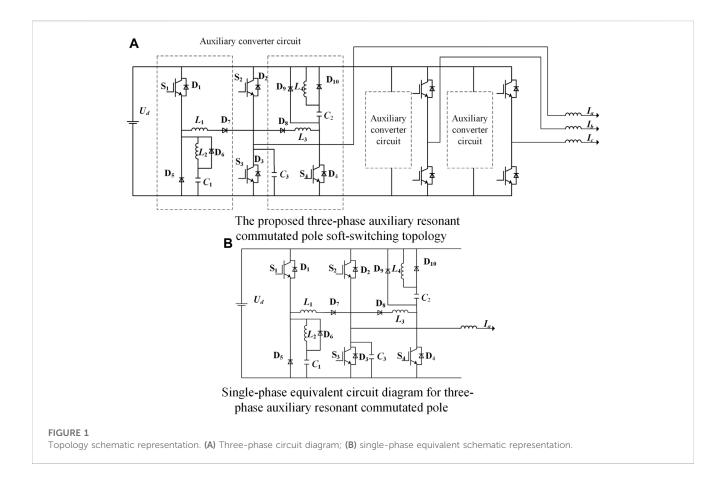

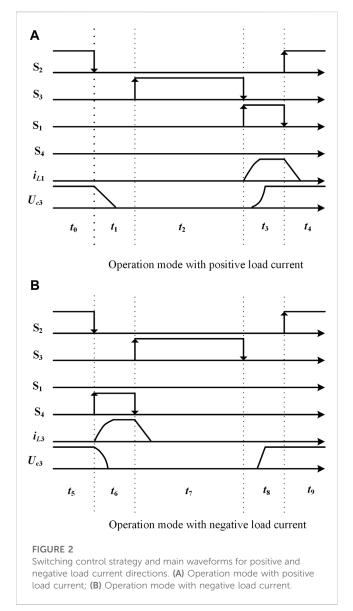

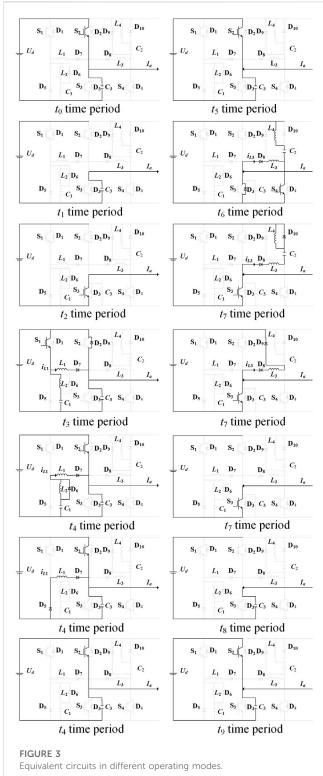

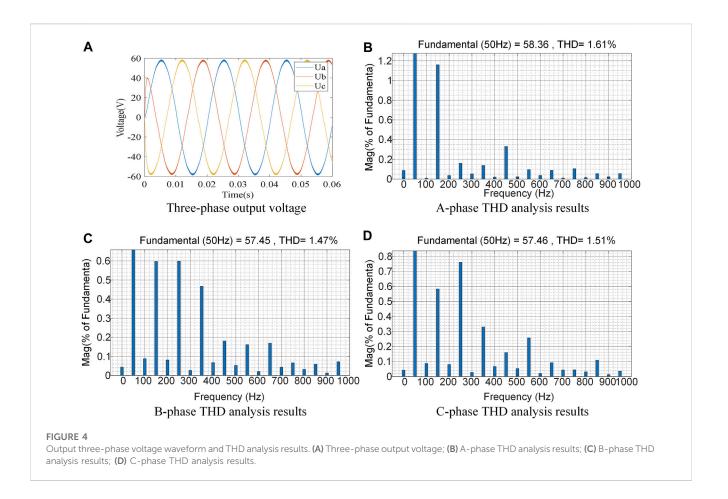

- Topology and control strategy optimization of an auxiliary resonant commutated pole-based, soft-switching grid-connected inverter

- Chuang Liu and Yanping Wang

#### **OPEN ACCESS**

EDITED BY Jingyang Fang, Shandong University, China

REVIEWED BY

Bin Duan,

Shandong University, China

Tohid Rahimi,

Carleton University, Canada

Dehao Qin,

Clemson University, United States

\*CORRESPONDENCE

Yetong Han,

2000665@stu.neu.edu.cn

SPECIALTY SECTION

This article was submitted to Smart Grids,

a section of the journal Frontiers in Energy Research

RECEIVED 23 September 2022 ACCEPTED 31 October 2022 PUBLISHED 13 January 2023

#### CITATION

Han Y, Ma D and An Q (2023), A switching control method based on a new model considering parasitic capacitance for LLC. *Front. Energy Res.* 10:1052004. doi: 10.3389/fenrg.2022.1052004

#### COPYRIGHT

© 2023 Han, Ma and An. This is an openaccess article distributed under the terms of the Creative Commons

Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.

## A switching control method based on a new model considering parasitic capacitance for LLC

Yetong Han<sup>1</sup>\*, Dazhong Ma<sup>1</sup> and Qingpeng An<sup>2</sup>

$^1\!\text{College}$  of Information Science and Engineering, Northeastern University, Shenyang, China,  $^2\!\text{Changguang}$  Satellite Technology Co., Ltd., Changchun, China

LLC converters are used for linking renewable energy and smart grids. However, the output is higher than the reference caused by its own characteristics, especially in the light load, and the output is limited. A new control method is proposed in this paper based on a new model considering parasitic capacitance, which plays a vital role in keeping the output constant in the light load conditions and widening the output range. In addition, the definition of the light load is given in this paper, which ensures an accurate control. In the switching process, a transition period is set to avoid the components from being damaged due to sudden switching and ensures a smooth output and the stability of the control. Finally, this control method based on the new model is proved valid on a 400 V-36 V-1 kw prototype.

KEYWORDS

DC-DC converter, half bridge, full bridge, digital control, topological changes

#### 1 Introduction

As smart grids advanced, great challenges were faced with power electronic devices (Hu et al., 2022; Wang et al.). The converter connects the smart grid to renewable energy, which requires the output constant, high power density, and high efficiency (Ma et al., 2022). DC–DC converters have two types on account of the transformer (Wang et al., 2022b; Hu et al., 2022). The non-isolated converters are applied to this solution, where the input and output have little difference. The isolated DC–DC converters are applied when the input and output greatly differ in value. Considering the bidirectional energy, DAB has a symmetrical structure that includes an inductor and a transformer (Huang et al., 2016; Liao et al., 2021). In addition, there was too much loss due to the limited range of soft-switching and reflux power, which can strengthen the reactive power (Song et al., 2018; Jeung and Lee, 2019). In Lu et al. (2018), a new topology was proposed to achieve soft-switching and ensure stability but backflow power was not addressed. A new control method that mixes power balance and unified phase shift was discussed, but only the current spike was optimized and additional losses were added (Hou et al., 2019). Although there are many ways to reduce the loss, the problems caused by the structure are not

completely solved. Compared with DAB, LLC has many advantages such like soft-switching, less power loss, and lower stress.

The LLC converter is widely used as an intermediate link in the transmission of energy to keep the voltage constant, which can achieve soft-switching due to its topology. There are one capacitance and two inductors that cause the current flow through the resonance cavity before voltage in this topology (Lee et al., 2014). Many problems come with advantages, such as the loss of the diodes. The transformer current sensing triggers the drive signal for the synchronous rectifier to reduce loss (Zhang et al., 2012). In addition, the transformer coil is added to eliminate the influence of excitation inductance so as to obtain an accurate synchronous rectification conduction time (Wang K. et al., 2022). The additional driver circuits in the aforementioned method also add new losses. By analyzing the small-signal characteristics of the resonant capacitor, the control method has been proposed for precise output voltage (Kang et al., 2017). Hence, digital control is used to avoid extra loss. The drain-tosource voltage of the synchronous rectifier is detected for the synchronous rectifier, but the current caused by the electromagnetic interference can be rough (Feng et al., 2010) By the pulse width-locked loop to get the synchronous rectifier conduction time, the diodes loss is diminished (Feng et al., 2013). Although the proposed control method has a fast reaction speed, the programmer is too complex to finish hard (Li et al., 2020). The reference is lower than the output voltage when the light load condition, the hybrid-adjustable switching-frequency-duty-cycle modulation, is proposed for adjusting the output and improving efficiency (Awasthi et al., 2021). A two-stage voltage modular for LLC converters is discussed by Fei et al. (2017), which can reduce the loss of switches, but add extra circuit loss. In addition, one method is adjusted to avoid noise in the light load condition (Yoon et al., 2018). The commutation direction can be obtained by analyzing the phase between switches to reduce the loss (Kundu et al., 2017). The two stages of converters based on the full load condition are given to the lower output voltage, which is applied to a meagre output (Ahmed et al., 2017). The new topology has been applied for widening the output voltage range but with the addition of an extra loss (Xue et al., 2021). The addition of a switch and a capacitor to is provided to improve efficiency (Lee et al., 2015), and this paper proposes to add SCC to the topology for keeping voltage (Hu et al., 2014). But the loss has been increased invisibly. Meanwhile, the LLC converter has a DC bias in the reversed mode. The symmetric topology called CLLC is proposed for reducing the deviation (Jung et al., 2013). The LLC and DAB converter are combined for dismissing the DC bias with complicated calculations (Liu et al., 2017). In addition, an extra inductor is eliminated to the DC bias in the reversed mode (Jiang et al., 2015), which is adopted in this paper, and a bidirectional three-level LLC resonant converter is given for a widened output (Jiang et al., 2016). The DC bias is eliminated by controlling the synchronous rectification signal, whereas it is too complex to be applied (Li et al., 2022; Li et al., 2022).

According to the aforementioned disadvantages, a switching control method for bidirectional LLC converters is proposed under light load conditions to improve the efficiency and keep the output constant and widen the output range. This paper contributes the following.

- One LLC converter model with parasitic capacitance is discussed, which can more accurately describe the situation, especially under the light load. The gain curve of this more realistic model is more accurate than that of the traditional model.

- 2) A control method is presented to make the output voltage close to the reference value and improve the efficiency under the light load, which includes two modes. The HB mode and FB mode are applied in this paper for maintaining the output voltage and widening the output range.

- 3) The definition of the light load is given in this paper, which is calculated by the gain curve of this new model. The HB and FB switching points vary under different load conditions for precise control. In addition, the switching period is adjusted to ensure the output smoothly and the stability of the control.

The paper is organized as follows. The new model considering parasitic capacitance is given in Section 2. The control method based on this and the definition of the light load is discussed in Section 3. Also, the principle is proved valid in Section 4 by a 400 V-36 V-1 kW prototype.

## 2 The model considering the parasitic capacitance

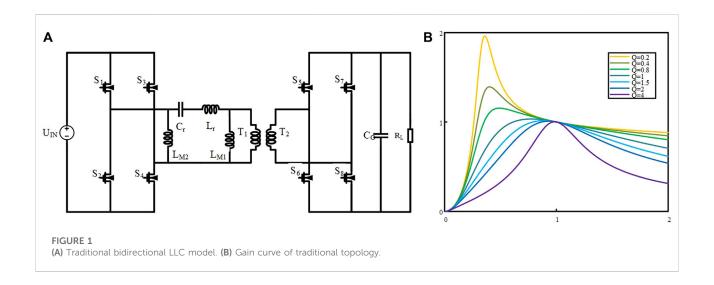

#### 2.1 The traditional model

There are two inductances that play an essential role in excitation, while another one and capacitance are in resonance. The forwarding mode is only mentioned, and the forwarding mode and reversed mode have the same state due to a symmetrical topology, as shown in Figure 1A. The gain curve of this topology is shown in Figure 1B. The soft-switching is achieved on the right of peak, an ideal operating area for the LLC converter. The peak goes down with the increasing load. The PI controller has been used in this model, which adjusts the output voltage by adjusting the switching frequency. The frequency is varied on the basis of the gain curve: the switching frequency increases when the load decreases. The duty ratio maintains 50%, and S1 and S2 keep complementary, the same as S3 and S4. The synchronous rectification strategy, which reduces the switching loss, is that the secondary switches are controlled by the PI controller, and

the drive signal frequency of those switches keeps pace with the primary switches.

Many problems are faced in the traditional model, especially at the light load condition, where the output voltage is limited by its character. The voltage is higher than the reference, which is settled in advance. When the frequency increases to a certain value, the voltage increases instead, which is inconsistent with the obtained gain curve. Therefore, a new model has been established so that the traditional model runs counter to the reality under the light load condition.

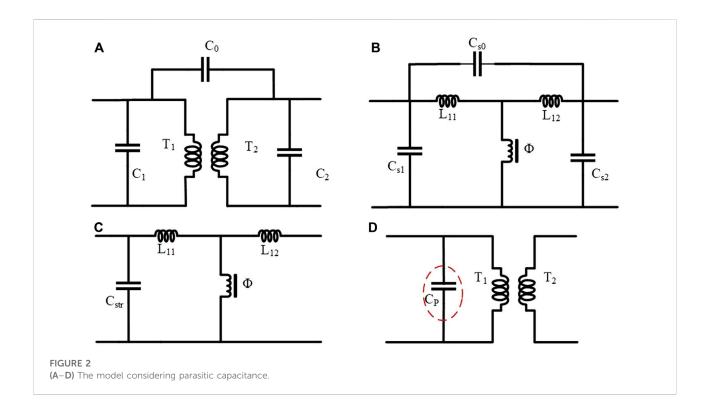

#### 2.2 The model with parasitic capacitance

The parasitic capacitance of the transformer is considered in this new model, which is more realistic than the traditional model. The transformer has two windings and stray capacitances, C<sub>1</sub> and C<sub>2</sub>, which are the self-capacitances of the transformer. C<sub>0</sub> is the mutual capacitance between the primary and secondary sides. Generally, the parasitic resistances of windings are ignored due to the value being too small, as shown in Figure 2A. The secondary side is converted to the primary side, where the stray capacitances are expressed as in Eq. 1, and the windings are replaced by the inductance and magnetic core in Figure 2B. The stray capacitance can be simplified as in Eq. 2 which is calculated by the two-port net approach (Lu et al., 2003) since the effort of C<sub>s0</sub> is insignificant. The SR junction capacitance is included in this model, and the parasitic capacitance can finally be described by Eq. 3. The capacitance circled in red is equivalent to the resulting parasitic capacitance in Figure 2D.

$$\left\{ \begin{array}{l} C_{s1} = C_1 + (1-n)C_0 \\ C_{s2} = n^2C_2 + n\left(n-1\right)C_0 \\ C_{s0} = nC_0 \end{array} \right. \tag{1}$$

$$C_{str} \approx C_{s1} + C_{s2} \tag{2}$$

$$C_P \approx C_{str} + C_{SR} \tag{3}$$

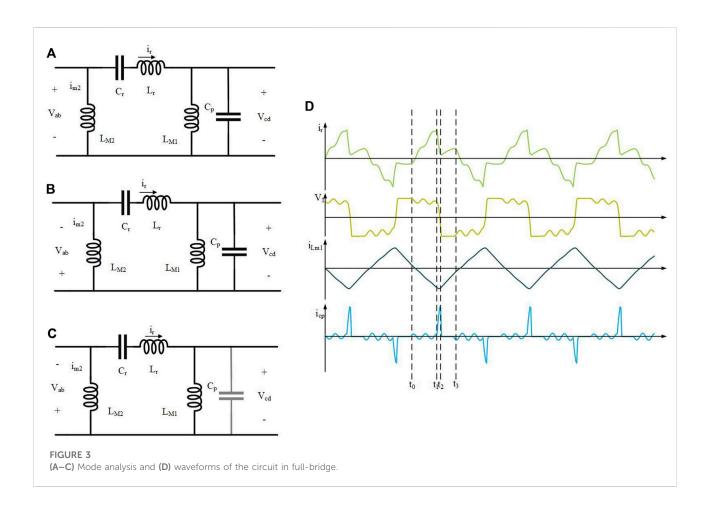

Some things are known before analyzing the LLC converter. The switching model is idealized without loss. In addition, the parasitic capacitance is placed in front of the transformer. Voltage commutation and current commutation exist in every cycle, in which the first half and the second half of the cycle are the same. Hence, only the half-cycle has been described based on the PI controller under the light load condition in the following.

Mode1 ( $t_0$ - $t_1$ ):  $S_1$  and  $S_4$  are turned on and  $S_2$  and  $S_3$  are turned off. At this period,  $L_r$  and  $C_p$  are in resonance owing to the value of the magnetic inductors being higher than the resonant inductor and the  $C_p$  being higher than the  $C_r$ . Therefore, the voltage of the resonance cavity is approximately zero, and the current increases gradually as shown in Figure 3A.

Mode2 ( $t_1$ - $t_2$ ): All switches are all off in this period as shown in Figure 3B. The voltage changes its direction, and voltage  $V_{ab}$  is reversed. The  $L_r$  and  $C_P$  keep resonance until the resonance current equals the magnetic current, as shown in Figure 3D.

Mode3 ( $t_2$ - $t_3$ ): The resonance current is smaller than the magnetic current. Therefore, the voltage drop is limited by the secondary side. In this period, the resonance cavity has been in resonance where  $C_r$  and  $L_r$  occur, and there is no other resonance. This mode lasts when the current in  $L_{M2}$  equals to the current in the resonator. The current reversal ends when this mode ends, and the second half period is the same due to the symmetric structure.

FHA is adopted for analyzing this model, which only leaves the fundamental component as the object of the study. The circuit, as shown in Figure 4, can be simplified, in which  $V_{ab}$  is the voltage at the midpoint of the two bridge arms and  $R_{\rm eq}$  is converting the actual load to the original side. The relationship between the input voltage and  $V_{ab}$  is described as

in Eq. 4, and the same can be the relationship between the output voltage and  $V_{cd}$  (Eq. 5).

$$V_{ab} = \frac{4V_{in}}{\pi} \sin \omega t \tag{4}$$

$$V_{cd} = \frac{4nV_{out}}{\pi} \sin \omega t \tag{5}$$

$$G = \frac{V_{out}}{V_{in}} = \frac{1}{\sqrt{\left(1 + \frac{1}{k} - \lambda x^2 - \frac{1}{kx} + \lambda\right)^2 + \left(x - \frac{1}{x}\right)^2 Q^2}}$$

(6)

$$Q = \frac{\sqrt{\frac{L_r}{C_r}}}{R_{eq}}, x = \frac{f_s}{f_r}, k = \frac{L_{M1}}{L_r}, \lambda = \frac{C_p}{C_r}$$

(7)

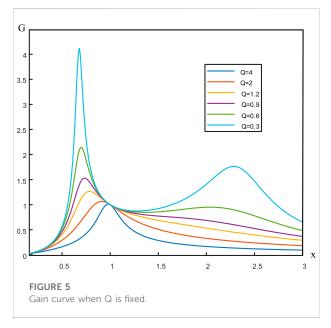

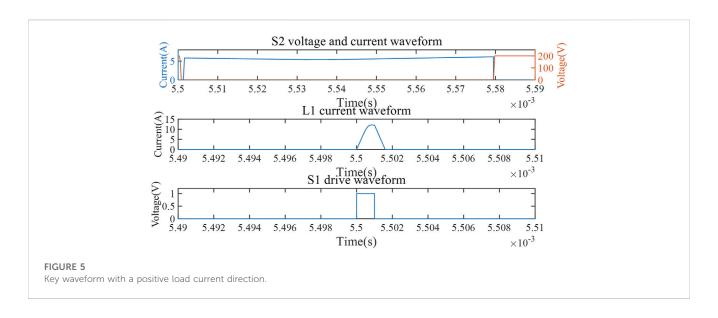

The voltage gain shown in Eq. 6 can be obtained by substituting the formula and simplifying it based on the voltage partition principle.  $\lambda$  is the ratio of the parasitic capacitance and resonant capacitance. Q is the quality factor, in which the value equals the ratio of the reactive power to active power. The switching frequency is standardized and shown as x, and the resonant frequency is taken as the reference. *k* is the ratio of the excitation inductance to the resonant inductance. The aforementioned parameters can be expressed by Eq. 7. The gain curve is shown in Figure 5, which has two voltage peaks. The circuit has come into the inductive region, where soft-switching can be achieved after the first peak, and the circuit works in this region generally. The secondary peak caused by the parasitic capacitance significantly impacts the output voltage, and the gain curve, when Q is fixed, is greater the parasitic capacitance, the higher the peak value.

## 3 The control method for the model considering the parasitic capacitance

The control method for the new model considering the parasitic capacitance is proposed to solve the problem under the light load condition, which includes two modes: half-bridge (HB) mode and full-bridge (FB) mode. This proposed control method is applied for widening the output range and is kept constant under the light load condition. According to Figure 5, the boundary between the light and heavy load can be calculated. Taking the derivative of the gain, Eq. 8 can be obtained.

$$F(x) = 2\lambda^2 x^8 + \left[\frac{2}{k}\left(1 + \frac{1}{k} + \lambda\right) - Q^2\right]x^2 - \left[2\lambda\left(1 + \frac{1}{k} + \lambda\right) - Q^2\right]x^6 - 2k^2$$

(8)

$$f(x) = R_{eq}^2 - \frac{L_r C_r}{2 \left[ C_p^2 + C_r C_p \left( 1 + \frac{L_M}{L_r} \right) \right]}$$

(9)

$$R_{eq} = \frac{8n^2}{\pi^2} * \frac{V_O^2}{P} \tag{10}$$

The curve with two spikes can be denoted as the light load, and the parameters are substituted into Eq. 9. The light and heavy loads are divided by Eq. 9.  $R_{\rm eq}$ , which is the equivalent resistance of the secondary side (10), belongs to the pure resistance load, as expressed by Eq. 10, which can be regarded as under the light load condition caused by the load being very small. After sampling the output voltage and current, the calculated resistance is substituted into Eq. 9. When the equation is

greater than zero, the load is deemed as the light one. When the frequency is at the left of the switching point, a traditional PI controller mentioned previously is adopted under light load conditions. At this period, the topology is in the FB mode, in which  $S_3$  and  $S_4$  keep in sync with  $S_2$  and  $S_1$ . The topology becomes HB mode when the switching frequency is higher than the switching point.

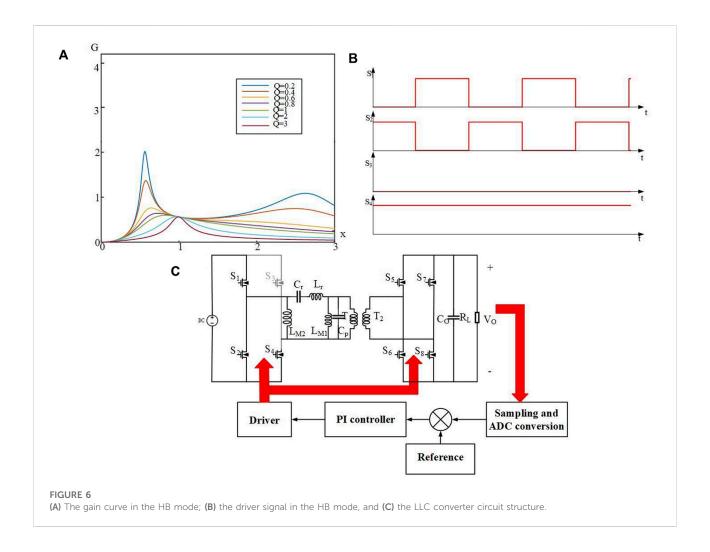

$\rm S_3$  keeps off normally, while  $\rm S_4$  keeps on in the HB mode, as shown in Figure 6A. The first bridge arm has maintained 50% duty approximately and remained complementary, and the frequency of switches is controlled according to the gain curve shown in Figure 6B.  $\rm V_{ab}$  becomes half in the FB mode. The secondary side switches are consistent with the primary side in frequency as a synchronous rectification scheme. The working state of the resonator in the HB mode is the same as that in the FB mode, in which the parasitic capacitance and resonance are in resonance before current commutation.

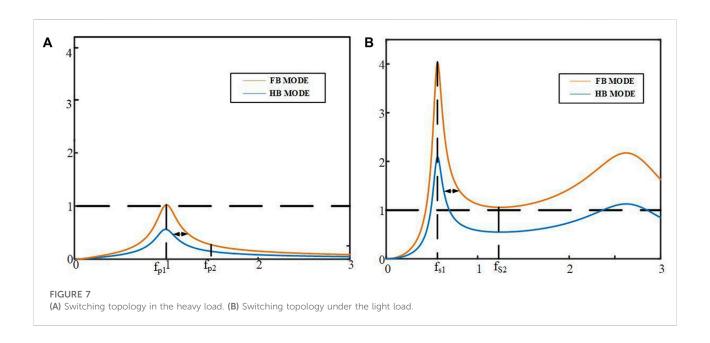

When switching the modes, the output voltage is kept constant without a giant ripple so that the ratio of the voltage and frequency tends to be zero. The ratio is equal to the value of the derivative approximately. In the heavy load, Eq. 8 has only one solution greater than zero, which is the minimum switching frequency. The maximum switching frequency related to the gain range of the output is artificially limited and is defined as  $f_{\rm P2}$ . If the output voltage is required to be large, the value of  $f_{\rm P2}$  is high, while if the output voltage is required to be small, the value of the  $f_{\rm P2}$  is low, as shown in Figure 7A. The switching frequency  $f_{\rm s}$  is

greater than  $f_{p1}$  at the heavy load when the switching frequency increases and the output voltage decreases.

When Eq. 8 equals zero under the light load, two of the solutions are chosen as the switching point, named  $f_{s1}$  and  $f_{s2}$ , respectively, as shown in Figure 7B. Due to the parameters in this circuit, there are three possible values of  $f_{s2}$ , greater than 1, less than 1, and equal to 1. It is of no sense to discuss the solutions that  $f_{s2}$  is less than or equal to 1 due to the reason of the extreme parameter values. The solution of  $f_{s2}$  greater than one is discussed as follows. Under the light load, the switching frequency,  $f_{s}$ , is greater than fs1 and less than  $f_{s2}$ , and the output voltage decreases with the increase of switching frequency. When the switching frequency is greater than  $f_{s2}$ , the output voltage increases with the increase in the switching frequency. Also, the switching points in the half-bridge mode and full-bridge mode are the same.

In the HB mode, the switching frequency decreases when the load increases. When the frequencies of  $S_1$  and  $S_2$  decline to  $f_{p1}$  or  $f_{s1}$  and the output is still less than the reference value, the mode is switched to the FB mode and the frequencies of  $S_1$  and  $S_2$  keep

varying. In the FB mode, the load decreases and the switching frequency increases. When the switching frequency increases to  $f_{\rm p2}$  or  $f_{\rm s2}$  and the reference value is less than the output voltage, the mode is switched to the HB mode.

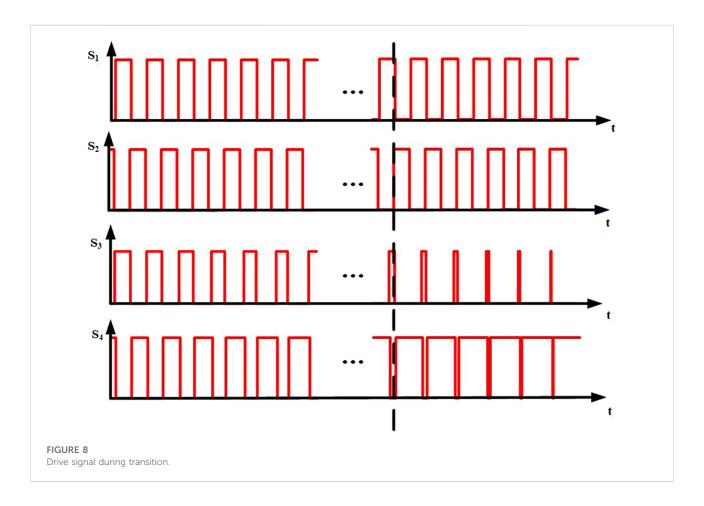

Suppose the signals of  $S_3$  and  $S_4$  vary in one period after arriving at the switching point, then the inductors lose the volt-second balance, and the components may be penetrated after reaching saturation due to the tremendous impact caused by topology mutation. Since the controller has a slow signal corresponding to this circuit, the switching time is extended to reduce the influence caused by topology change.

The duty cycle changes in the process of mode switching. The  $S_3$  duty cycle changes from 0 to 50%, and the  $S_4$  duty cycle changes from 100 to 50%. Mode switching is implemented in several cycles to prevent voltage spikes and current spikes in the changing process. In the variation,  $S_1$  and  $S_4$  end simultaneously in one cycle, while  $S_2$  and  $S_3$  end simultaneously, which is kept

TABLE 1 Detailed parameters in the prototype.

| Parameter             | Value                                 |

|-----------------------|---------------------------------------|

| Resonance inductor    | $L_{\rm r}=101~\mu H$                 |

| Resonance capacitance | $C_r = 24.6 \ \mu H$                  |

| Magnetic inductance   | $L_{\rm M1} = L_{\rm M2} = 606~\mu H$ |

| Ratio of transformer  | n = 12                                |

| Resonance frequency   | 100 k                                 |

|                       |                                       |

complementary to ensure that the circuit is running correctly, as shown in Figure 8. During transition, the switching frequencies of  $S_1$  and  $S_2$  continue to be regulated by the PI controller. The switching frequencies of  $S_1$  and  $S_2$  are adjusted without considering the duty cycle changes of  $S_3$  and  $S_4$  for maintaining the output constant. The switching frequency of the first arm bridge decreases with the increasing load and increases with the

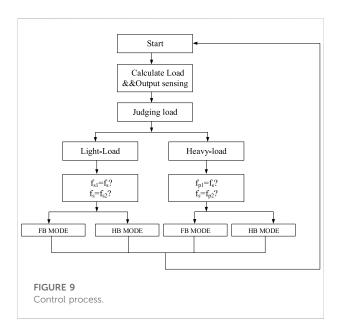

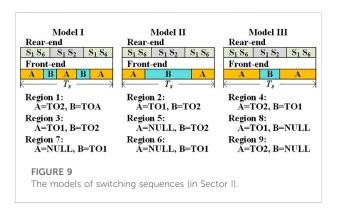

decreasing load. The overall control process is shown in Figure 9.

#### 4 The experiment

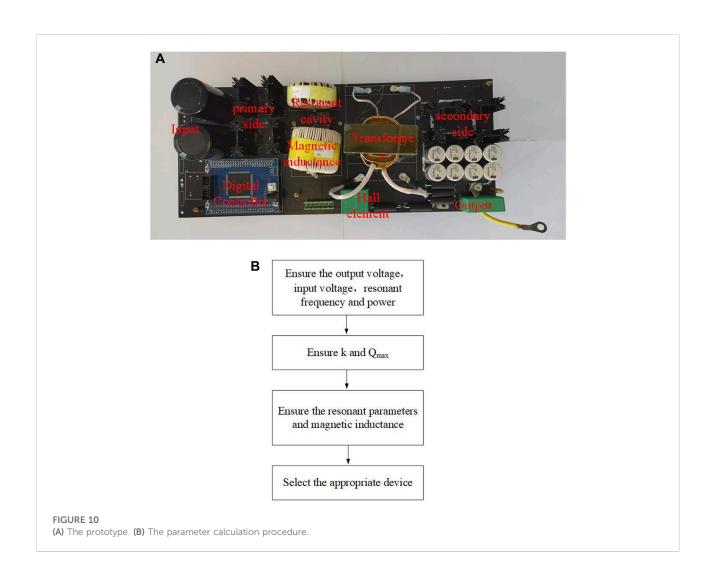

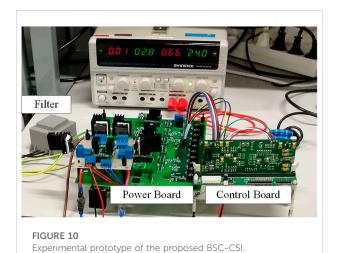

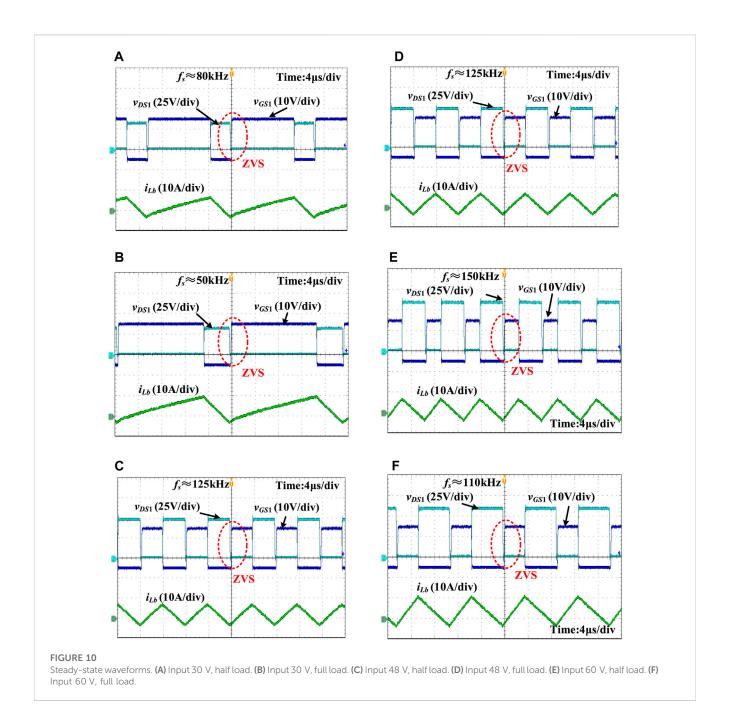

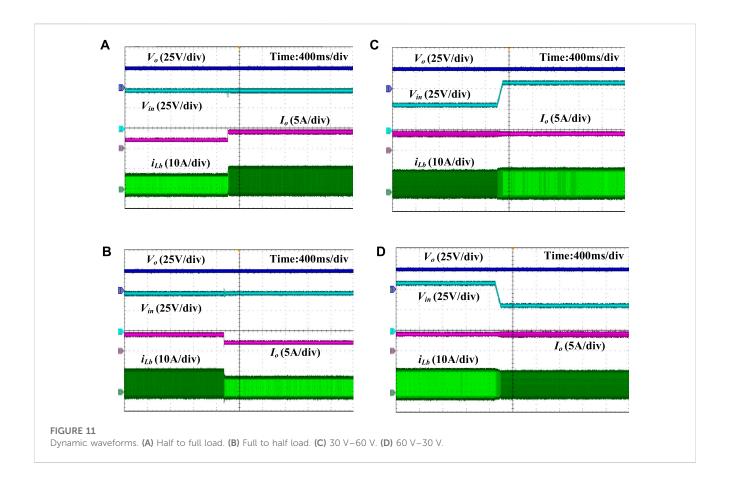

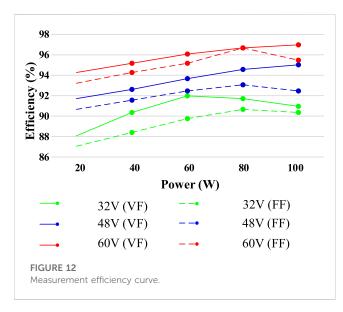

The prototype is connected to an energy storage device at one end and a smart grid at the other, as shown in Figure 10. The

input voltage is limited from 360~V to 440~V, and the output voltage is kept constant at 36~V. The maximum output current in the forwarding mode equals 27~A, and 2.5~A in the reversed mode, whereas the maximum power is 1~kW. The resonance frequency is set as 100~k, the same as the switching frequency in the full load in theory. Due to the components having parasitic parameters, the actual resonant frequency has some differences from the theoretical one. Considering the current and voltage

stress, the components have 2–3 times margin. The digital control can be more flexible in various situations compared with the analog control, with the computing power and speed required for existing integrated chips. In this prototype, DSP, TMS320F28335 (Tohid et al., 2018) published by Texas Instruments as the digital controller, plays a role that occurs in the driving signal, performing the digital to analog conversion, sampling unit, and so on. The switching frequency is calculated. The output current and voltage, which are sampled by the Hall element, are converted to a digital form by the analog to a digital converter in DSP. The main converter parameters are shown in Table 1. It is worth mentioning that the prototype is only for principle verification, so the power density is not considered in the design.

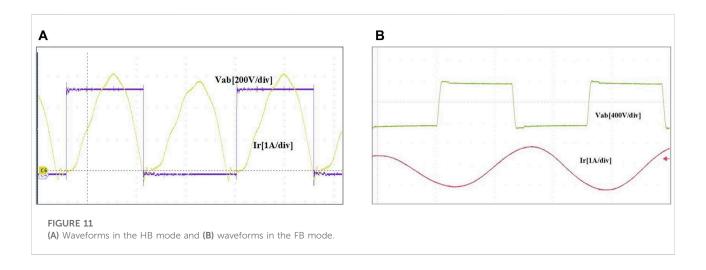

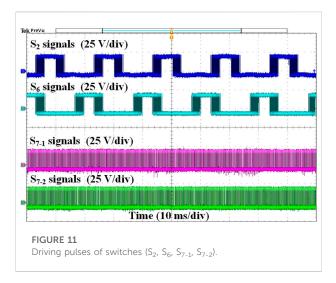

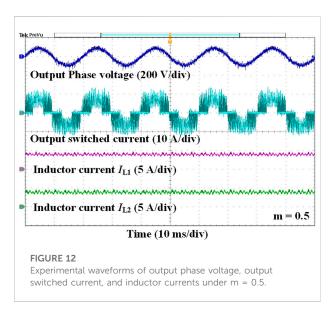

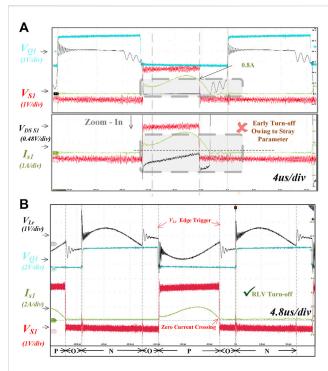

Figure 11A shows the waves, including the H-bridge voltage and the resonant current. The voltage is around 400 V in the HB mode, where  $S_3$  keeps 0% and  $S_4$  keeps 100% duty. Figure 11B shows the H-bridge voltage and current in the FB mode, where  $S_3$  and  $S_4$  keep 50% duty. The voltage varies from +400 V to -400 V. The modes are switched due to the input voltage and load variable.

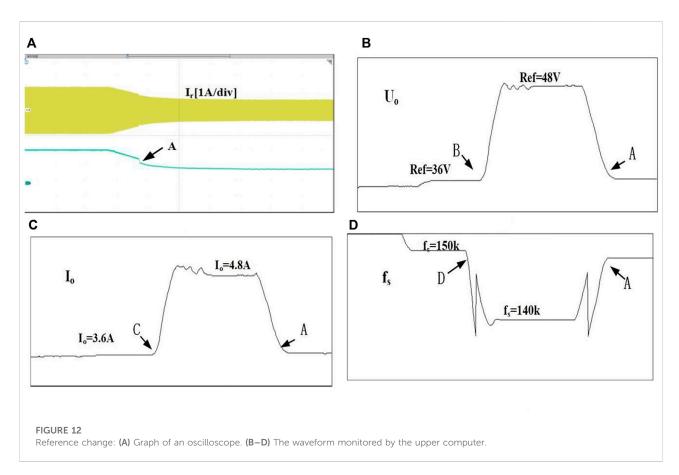

In Figure 12, the load is constant and the reference value is changed. Figure 12A shows the oscilloscope waveform, and Figures 12B-D show the waveforms displayed by the host computer. Point B, point C, and point D are simultaneous and the reference voltage changes from 36 V to 48 V. The reference value increases, the mode switches to full bridge mode, and the frequency drops. Point A indicates that the reference value changes from 48 V to 36 V. The reference value drops, switching from the FB mode to the HB mode. The mode is switched when the reference has been changed, and the output range is widened.

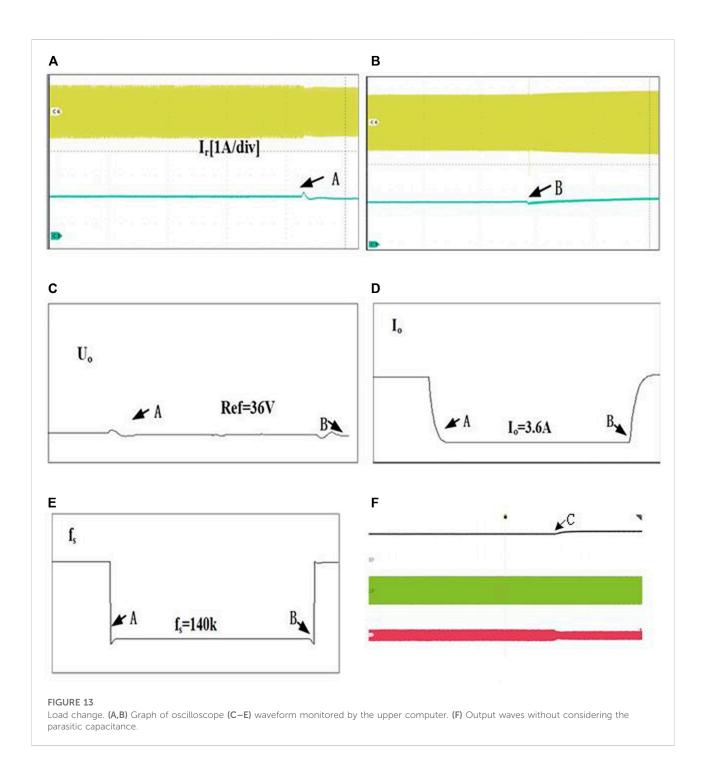

In Figure 13, the reference value is constant at 36 V and the load is changed. Figures 13A, B show the waveforms on the oscilloscope and Figures 13C–E show the waveforms on the host computer. At point A, the load decreases, the current decreases, and the converter is handed over from the FB mode to the HB mode. At point B, the load increases and the

converter is handed over from the FB mode to the HB mode. When the load changes, the output voltage transitions smoothly and can maintain the constant voltage under a light load. Although controlled by PI, the reaction speed is faster. A green wave indicates the voltage of the H-bridge, a red wave indicates the current of the resonator, and the black wave indicates the output voltage. At the C point, the load is decreased but the reference is kept constant. There is only switching frequency controlled by PI in the traditional control method.

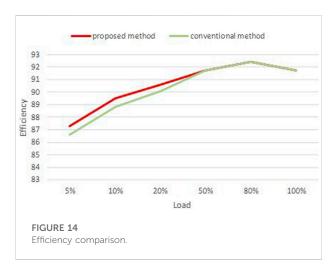

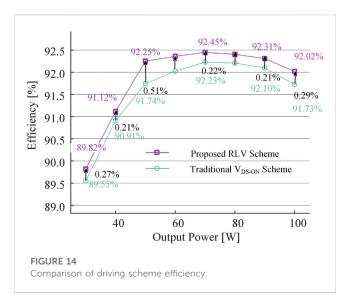

Compared with the conventional method, S<sub>1</sub> and S<sub>2</sub> are complementary conduction according to 50% duty cycle in the proposed method of the light load. S3 is kept always on and S4 is kept always off. Therefore, S3 and S4 have lower switching losses. Therefore, the efficiency is improved compared with the traditional method in the light load. The proposed control method is the same as the conventional method, and hence, the efficiency is the same. In Figure 14, the horizontal axis represents the load and the vertical axis represents efficiency. As the load increases, the efficiency gradually increases. The efficiency is the highest when the load reaches 80%, after which the efficiency decreases with the load. The loss can be divided into two types, the fixed loss and the variable loss. The fixed loss includes the transformer loss, the switching loss, and the line loss. Under the light load, the fixed loss accounts for a larger proportion, so the efficiency is low. As the load increases, the proportion of the fixed loss becomes smaller and smaller, with the highest efficiency at about 80% load. With the increase of load, the current increases, the heat loss increases, and the efficiency decreases.

#### 5 Conclusion

The control method is based on the new model considering parasitic capacitance, which plays a vital role in adjusting the output voltage and broadening the output range. In this paper, the model considering parasitic capacitance is more realistic than before, in which the gain curve has two spikes. In addition, the definition of the light load is given on the basis of the gain. Also, the switching frequency, which varies under different load conditions, has been adjusted depending on the gain curve by the PI controller, and there are two modes in this control: the HB mode and the FB mode. The output can be maintained constant under light load conditions and can be widened. The variation of the driving signal is also given to avoid topological mutation causing damage to other devices in transition. It is proven that the model and control method presented in this paper is effective in a 400V-36V-1 kW prototype. Compared with the previous methods, it can improve the efficiency and ensure the constant output voltage under the light load (Wang et al., 2022c).

#### Data availability statement

The original contributions presented in the study are included in the article/Supplementary Material. Further inquiries can be directed to the corresponding author.

#### **Author contributions**

All authors listed have made a substantial, direct, and intellectual contribution to the work and approved it for publication.

#### **Funding**

This research was funded by the Fundamental Research Funds for the Central Universities grant number N2204007.

#### References

Ahmed, M. H., Fei, C., Lee, F. C., and Li, Q. (2017). 48-v voltage regulator module with PCB Winding Matrix Transformer for future data centers. *IEEE Trans. Ind. Electron.* 64 (12), 9302–9310. doi:10.1109/TIE.2017.2711519

Awasthi, A., Bagawade, S., and Jain, P. K. (2021). Analysis of a hybrid variable-frequency-duty-cycle-modulated low-Q LLC resonant converter for improving the light-load efficiency for a wide input voltage range. *IEEE Trans. Power Electron.* 36 (7), 8476–8493. doi:10.1109/TPEL.2020.3046560

Fei, C., Ahmed, M. H., Lee, F. C., and Li, Q. (2017). Two-stage 48v-12v/6v-1.8v voltage regulator module with dynamic bus voltage control for light-load efficiency improvement. *IEEE Trans. Power Electron.* 32 (7), 5628–5636. doi:10.1109/TPEL.2016.2605579

Feng, W., Huang, D., Mattavelli, P., Fu, D., and Lee, F. C. (2010). "Digital implementation of driving scheme for synchronous rectification in llc resonant converter," in 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12-16 September 2010.

Feng, W., Mattavelli, P., and Lee, F. C. (2013). Pulsewidth locked loop (PWLL) for automatic resonant frequency tracking in LLC DC–DC transformer (LLC -dcx). *IEEE Trans. Power Electron.* 28 (4), 1862–1869. doi:10.1109/TPEL.2012.2210912

Hou, N., Song, W., Li, Y., Zhu, Y., and Zhu, Y. (2019). A comprehensive optimization control of dual-active-bridge dc-dc converters based on unified-phase-shift and power-balancing scheme. *IEEE Trans. Power Electron.* 34, 826–839. doi:10.1109/TPEL.2018.2813995

Hu, X., Zhang, H., Ma, D., and Wang, R. (2022). Hierarchical pressure data recovery for pipeline network via generative adversarial networks. *IEEE Trans. Autom. Sci. Eng.* 19 (3), 1960–1970. doi:10.1109/TASE.2021.3069003

Hu, X., Zhang, H., Ma, D., Wang, R., and Tu, P. (2022). Small leak location for intelligent pipeline system via action-dependent heuristic dynamic programming. *IEEE Trans. Ind. Electron.* 69, 11723–11732. doi:10.1109/TIE.2021.3127016

Hu, Z., Qiu, Y., Wang, L., and Liu, Y. (2014). An interleaved LLC resonant converter operating at constant switching frequency. *IEEE Trans. Power Electron.* 29 (6), 2931–2943. doi:10.1109/TPEL.2013.2273939

Huang, J., Wang, Y., Li, Z., and Lei, W. (2016). Unified triple-phase-shift control to minimize current stress and achieve full soft-switching of isolated bidirectional dc-dc converter. *IEEE Trans. Ind. Electron.* 63, 4169–4179. doi:10.1109/TIE.2016.2543182

#### Conflict of interest

QA was employed by Changguang Satellite Technology Co., Ltd.

The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

#### Publisher's note

All claims expressed in this article are solely those of the authors and do not necessarily represent those of their affiliated organizations, or those of the publisher, the editors, and the reviewers. Any product that may be evaluated in this article, or claim that may be made by its manufacturer, is not guaranteed or endorsed by the publisher.

Jeung, Y., and Lee, D. (2019). Voltage and current regulations of bidirectional isolated dual-active-bridge dc-dc converters based on a double-integral sliding mode control. *IEEE Trans. Power Electron.* 34, 6937–6946. doi:10.1109/TPEL.2018.2873834

Jiang, T., Zhang, J., Wu, X., Sheng, K., and Wang, Y. (2015). A bidirectional LLC resonant converter with automatic forward and backward mode transition. *IEEE Trans. Power Electron.* 30 (2), 757–770. doi:10.1109/TPEL.2014.2307329

Jiang, T., Zhang, J., Wu, X., Sheng, K., and Wang, Y. (2016). A bidirectional three-level LLC Resonant converter with PWAM control. *IEEE Trans. Power Electron.* 31 (3), 2213–2225. doi:10.1109/TPEL.2015.2438072

Jung, J., Kim, H., Ryu, M., and Baek, J. (2013). Design methodology of bidirectional CLLC resonant converter for high-frequency isolation of DC distribution systems. *IEEE Trans. Power Electron.* 28 (4), 1741–1755. doi:10.1109/TPEL.2012.2213346

Kang, S., and Cho, B. (2017). Digitally implemented charge control for llc resonant converters. *IEEE Trans. Ind. Electron.* 64 (8), 6159–6168. doi:10.1109/TIE.2017.2682801

Kundu, U., Yenduri, K., and Sensarma, P. (2017). Accurate zvs analysis for magnetic design and efficiency improvement of full-bridge llc resonant converter. *IEEE Trans. Power Electron.* 32 (3), 1703–1706. doi:10.1109/TPEL.2016.2604118

Lee, I., and Moon, G. (2014). The K-Q analysis for an LLC series resonant converter. *IEEE Trans. Power Electron.* 29 (1), 13–16. doi:10.1109/TPEL.2013. 2255106

Lee, J., Kim, J., Kim, J., Baek, J., and Moon, G. (2015). A High-efficiency PFM half-bridge converter utilizing a half-bridge LLC converter under light load conditions. *IEEE Trans. Power Electron.* 30 (9), 4931–4942. doi:10.1109/TPEL.2014.2365625

Li, H., Wang, S., Zhang, Z., Zhang, J., Zhu, W., Ren, X., et al. (2022). A bidirectional synchronous/asynchronous rectifier control for wide battery voltage range in sic bidirectional llc chargers. *IEEE Trans. Power Electron.* 37 (5), 6090–6101. doi:10.1109/TPEL.2021.3126886

Li, H., Wang, S., Zhang, Z., Zhang, J., Zhu, W., Ren, X., et al. (2022). An impedance-based digital synchronous rectifier driving scheme for bidirectional high-voltage sic llc converter. *IEEE Trans. Ind. Electron.* 69 (11), 11314–11323. doi:10.1109/TIE.2021.3127037

Li, H., Zhang, Z., Wang, S., Tang, J., Ren, X., and Chen, Q. (2020). A 300-kHz 6.6-kW sic bidirectional LLC onboard charger. *IEEE Trans. Ind. Electron.* 67 (2), 1435–1445. doi:10.1109/TIE.2019.2910048

- Liao, Y., Xu, G., Sun, Y., Peng, T., Su, M., Guo, B., et al. (2021). Single-stage DAB-LLC hybrid bidirectional converter with tight voltage regulation under DCX operation. *IEEE Trans. Ind. Electron.* 68, 293–303. doi:10.1109/TIE.2020. 2965495

- Liu, C., Liu, H., Cai, G., Cui, S., Liu, H., and Yao, H. (2017). Novel hybrid LLC resonant and DAB linear DC-DC converter: Average model and experimental verification. *IEEE Trans. Ind. Electron.* 64 (9), 6970–6978. doi:10.1109/TIE.2017.2682784

- Lu, H. Y., Zhu, J. G., and Hui, S. Y. R. (2003). Experimental determination of stray capacitances in high frequency transformers. *IEEE Trans. Power Electron.* 18 (5), 1105–1112. doi:10.1109/TPEL.2003.816186

- Lu, Y., Wu, Q., Wang, Q., Liu, D., and Xiao, L. (2018). Analysis of a novel zero-voltage-switching bidirectional dc/dc converter for energy storage system. *IEEE Trans. Power Electron.* 33, 3169–3179. doi:10.1109/TPEL.2017.2703949

- Ma, D., Cao, X., Sun, C., Wang, R., Sun, Q., Xie, X., et al. (2022). Dual-predictive control with adaptive error correction strategy for AC microgrids. *IEEE Trans. Power Deliv.* 37 (3), 1930–1940. doi:10.1109/TPWRD.2021.3101198

- Song, W., Hou, N., and Wu, M. (2018). Virtual direct power control scheme of dual active bridge dc-dc converters for fast dynamic response. *IEEE Trans. Power Electron.* 33, 1750–1759. doi:10.1109/TPEL.2017.2682982

- Tohid, R., Wagle, B., Shirzad, S., Diehl, P., Serio, A., Kheirkhahan, A., et al. (2018). Asynchronous execution of Python code on task-based runtime systems. Ithaca: IEEE, 37–45.

- Wang, K., Wei, G., Wei, J., Wu, J., Wang, L., and Yang, X. (2022a). Current detection and control of synchronous rectifier in high-frequency LLC Resonant Converter. *IEEE Trans. Power Electron.* 37 (4), 3691–3696. doi:10.1109/TPEL.2021.3119770

- Wang, R., Jiang, S., Ma, D., Sun, Q., Zhang, H., and Wang, P. (2022b). The Energy Management of multi-port energy router in smart home. *IEEE Trans. Consum. Electron.* 1, 1. doi:10.1109/TCE.2022.3200931

- Wang, R., Li, W., Sun, Q., Li, Y., Gui, Y., and Wang, P. (2022c). Fully distributed dynamic edge-event-triggered current sharing control strategy for multi-bus dc microgrids with power coupling. *IEEE Trans. Ind. Inf.* 2022, 1–11. doi:10.1109/TII. 2022.3188352

- Xue, B., Wang, H., Liang, J., Cao, Q., and Li, Z. (2021). Phase-shift modulated interleavedllc converter with ultrawide output voltage range. *IEEE Trans. Power Electron.* 36 (1), 493–503. doi:10.1109/TPEL.2020.3001126

- Yoon, H., Lee, H., Ham, S., Choe, H., and Kang, B. (2018). Off-time control of <italic&gt;LLC&dt;/italic&gt; resonant half-bridge converter to prevent audible noise generation under a light-load condition. *IEEE Trans. Power Electron.* 33 (10), 8808–8817. doi:10.1109/TPEL.2017.2774840

- Zhang, J., Wang, J., Zhang, G., and Qian, Z. (2012). A hybrid driving scheme for full-bridge synchronous rectifier in LLC resonant converter. *IEEE Trans. Power Electron.* 27, 4549–4561. doi:10.1109/TPEL.2011.2180027

#### **OPEN ACCESS**

EDITED BY Hao Tian, University of Alberta, Canada

REVIEWED BY

Qiao Peng,

Sichuan University, China

Jiangfeng Wang,

Southeast University, China

\*CORRESPONDENCE Xingjian Zhao, ⋈ 202134949@mail.sdu.edu.cn

#### SPECIALTY SECTION

This article was submitted to Smart Grids,

a section of the journal Frontiers in Energy Research

RECEIVED 11 November 2022 ACCEPTED 28 November 2022 PUBLISHED 19 January 2023

#### CITATION

Zhao X, Gao X, Zhou X and Gao F (2023), Optimization strategy and control technology of four-port SOP for distribution network with PV and BESS. *Front. Energy Res.* 10:1095607. doi: 10.3389/fenrg.2022.1095607

#### COPYRIGHT

© 2023 Zhao, Gao, Zhou and Gao. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.

## Optimization strategy and control technology of four-port SOP for distribution network with PV and BESS

Xingjian Zhao<sup>1</sup>\*, Xiongying Gao<sup>2</sup>, Xin Zhou<sup>2</sup> and Feng Gao<sup>1</sup>

<sup>1</sup>School of Control Science and Engineering, Shandong University, Jinan, China, <sup>2</sup>Yangzhou Huading Electric Co., Ltd., Yangzhou, China

This paper proposes a four-port soft open point (FSOP) with photovoltaic (PV) and battery energy storage systems (BESS) and its optimization strategy and control technology. Combining PV output, BESS characteristics, peak and valley electric charges, transformer operation efficiency, and soft open point (SOP) characteristics, the operation criteria under different operating conditions are formulated to improve the economy of the distribution network. In this paper, the power distribution optimization algorithm is established based on the transformer consumption characteristic model and the equal consumption incremental rate criterion to improve the power utilization rate and the system's economy. The system doesn't require an additional central controller and transmits control signals through the DC link of FSOP to realize the coordinated operation of all ports. The simulation results show that the system and the optimization strategy can realize the system's coordinated operation and improve the distribution network's economy.

#### KEYWORDS

PV, BESS, SOP, the consumption characteristic model, the power distribution optimization algorithm, no central controller

#### 1 Introduction

The increasingly diversified load and power demand make the AC distribution network have great problems in safety, reliability, economic applicability, and distribution efficiency (Ji, 2019). With the adjustment of the energy structure and the development of the power system, distributed PV, BESS, and new power electronic equipment are more and more widely used in the power system, which makes the distribution network have more abundant and active regulation capability. Among them, SOP, as a fully controlled power electronic device, has attracted the attention of many scholars.

Access to distributed PV and BESS effectively alleviates the problem of resource shortage and large load fluctuation of the distribution network (Conti, 2012; Bloemink, 2013; Rueda, 2013). However, when they are connected to the distribution network, they are all planned, designed and operated independently, there is a lack of coordination between the systems, as well as the problem of converter redundancy, which leads to a

decrease in the economy and stability of the system. At the same time, the periodic characteristics of PV power generation and the periodic changes of power load make the power flow size and direction of the distribution network change at any time. Therefore, the low-voltage distribution network suffers from large fluctuations in transmission power, difficulties in ensuring transformer operating efficiency, high operating costs, and difficulties in matching power generation and consumption (Verzijlbergh, 2014; Huang, 2015). It is not easy to ensure the economic applicability and distribution efficiency of low-voltage distribution networks.

The power distribution-oriented SOP has flexible, fast, and accurate power exchange control and power flow optimization capabilitiy (Chen, 2020; Wang, 2022; Zhou, 2022), and can realize the integrated coordination and optimization management of "Generation-Grid-Load-Storage" 2013; Wang, 2016b; Zeng, 2016). It enables the AC distribution network to balance safety and reliability, economic applicability and distribution efficiency (Wang, 2017; Kashani, 2019; Wang, 2020). Wang (2016a), Xue (2020), and Li (2021) studied the optimal operation and cooperative control strategy of flexible distribution network based on SOP. And the results show that SOP can improve the system power flow and reduce system loss. Wang (2017) studied the SOP siting and capacity fixing problem, and the research results showed that the reasonable configuration of SOP can effectively improve the economy of distribution network. The research on multi-port control of SOP of Huang (2019) and Wu (2019) shows that stable DC link voltage is a prerequisite for stable operation of multiport system containing SOP, and that with SOP control, the system can achieve power flow between multiple port.

Many scholars have studied the optimal operation of systems containing SOP and proved the effectiveness of SOP in the optimal operation of distribution networks. However, most of the studies are focused on the location of SOP and the setting of BESS capacity. There is little research on the connection mode and collaborative control of PV, BESS, and SOP. The optimization of the operation of the transformers connected to the SOP is also rarely considered.

Based on the above research and analysis, this paper proposes to connect PV and BESS to the SOP's DC link to form a FSOP. Compared with the independent grid connection of distributed power sources, FSOP can save cost by reducing the number of converters and replacing multiple small capacity BESSs with one large capacity BESS. On the premise of comprehensive consideration of PV output, the efficiency characteristics of transformers, and peak and valley electric charges, this paper proposes a novel power distribution optimization algorithm. The algorithm uses the power regulation function of SOP to realize the cooperative operation of multiple converters, and establishes an optimization model to improve the economy and stability of the distribution network. In the power distribution optimization algorithm, an optimal scheduling method based on equal

consumption incremental rate criterion is established to improve the economy and stability of the system. In the multi-converters collaborative control strategy, the DC link of FSOP is used as the signal transmission path to realize the cooperative control of each unit without the central controller. Finally, the effectiveness of the proposed optimization method is verified by Matlab/SIMULINK.

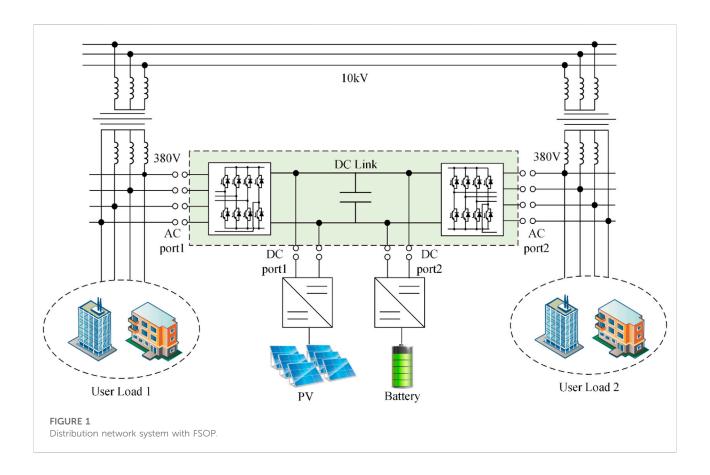

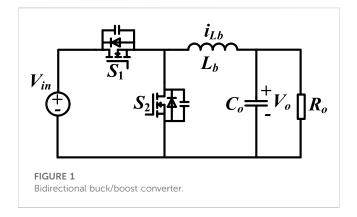

#### 2 The structure of four-port soft open point for distribution network with photovoltaic and battery energy storage systems

In this paper, we propose a four-port soft open point, as shown in Figure 1. Two AC ports are directly connected to the distribution network. Two DC ports are led from the DC link of the FSOP and connected to PV and BESS. As shown in Figure 1, the device is connected to two transformer rooms of the distribution network and connected to PV and BESS to form a small distribution network system. The system connects the four ports through a DC link to achieve power flow and regulation between the four ports, creating a hardware foundation for power transfer in time and space (Miu, 2012). In combination with the policy of peak and valley electric charges, the operation strategy is formulated to realize the coordinated operation of each unit, improve the operation efficiency of the system and the economic benefits.

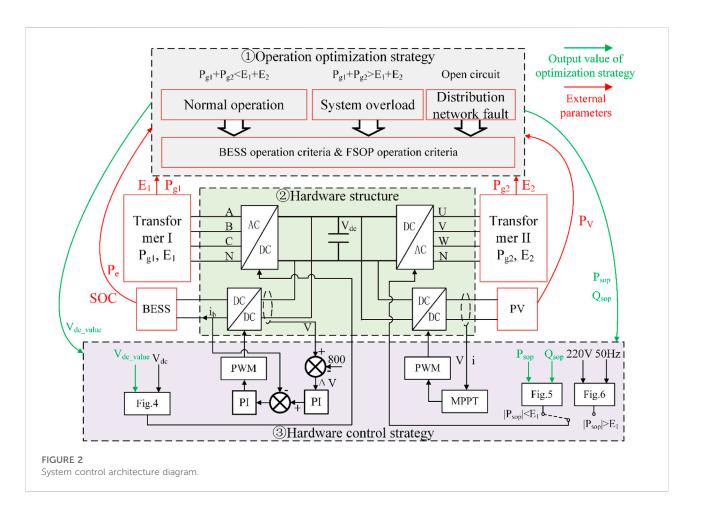

The system mainly includes transformers, FSOP, PV, BESS, user load, and etc. PV output is limited by natural resource conditions, which can be regarded as a relatively uncontrollable power supply to provide certain power support for the system. BESS is connected to the FSOP through a bidirectional DCDC converter, and can change the working state by adjusting the operation strategy to realize the load transfer in the time scale. Transformers can be regarded as the main power supply of the system, and the operation efficiency can be improved by adjusting the load rate. FSOP can change the working mode by changing the control strategy to realize the transfer of load at the spatial scale (Wang, 2013). The overall control architecture of the system is shown in Figure 2.

As shown in Figure 2, the part ① divides the system into different operation states. Then, according to PV output and the state of BESS, the optimal operation criteria is executed and the control signals are generated. The part will be described in detail in Section 3. The part ② represents the hardware structure of the four-port SOP proposed in this paper, which is the carrier of control and optimization operation strategies. The part ③ realizes the control of the four converters in the system based on the control signals generated by the part ①.First, FSOP controls the operation of the two AC/DC converters according to the control signal generated by the operation optimization strategy, and then controls the other two DC/DC

converters according to the voltage of DC link. Among them, 220 V and 50 Hz represent the standard value of mains voltage, and 800 represents a reference value, which can determine the control strategy of BESS by comparing with V. The Section 4 will describe this part in detail.

#### 3 System optimization layer

The system has four ports, which are connected through a DC link. This connection creates the basis for energy flow between the ports. At the same time, the coupling between each unit is enhanced and the difficulty of cooperative operation is increased. In order to realize the cooperative operation of each converter and realize the optimal scheduling of PV, BESS, and FSOP, it is necessary to formulate the optimal operation strategy of the system (Cao, 2016; Ding, 2011; Li, 2015; Zeng, 2016; Zhang, 2020; Zhao, 2015).

#### 3.1 Operation criteria

The purpose of formulating optimization strategy is to realize the stable and economic operation of the system by adjusting the operation state of each unit. Therefore, it is necessary to define the operation criteria of each unit first and then determine the system's overall operation strategy according to each unit's operational criteria. The operation criteria of BESS, PV, FSOP, and the equal consumption incremental criterion of the transformer will be introduced below.

To distinguish the operation state of the system, the following definitions are made in this paper. Transformer overload state means that the output power of the transformer exceeds the rated capacity. System overload state means that the total output power of two transformers exceeds the total rated capacity. Normal operation state means that the system is not overloaded.

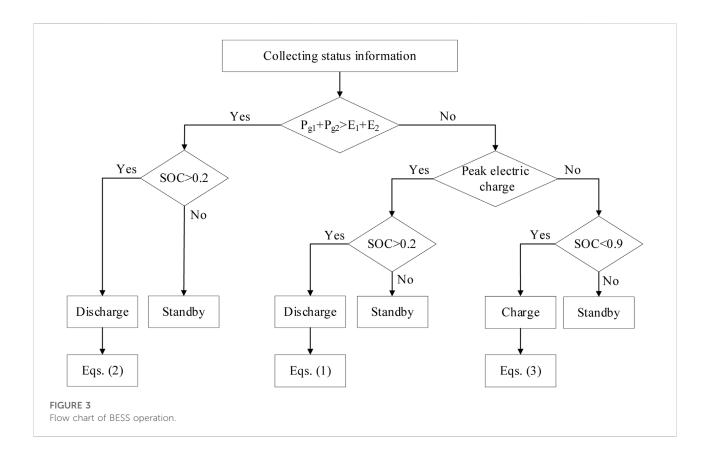

### 3.1.1 Battery energy storage systems operation criteria

BESS can transfer power consumption across time scales to reduce load fluctuations in distribution network and reduce operating costs. Therefore, this paper proposes a BESS charging and discharging operation criterion based on the state of charge (SOC), electricity price, and transformer overload state, as shown in Figure 3.

$$P_e = P_{cnmax} \tag{1}$$

$$P_e = min\{P_{cnmax}, P_{L1} + P_{L2} - E_1 - E_2 - P_V\}$$

(2)

$$P_e = min\{P_{cnmax}, -P_{L1} - P_{L2} + E_1 + E_2 + P_V - P_{excess}\}$$

(3)

Where,  $P_e$  represents the actual charging and discharging power of BESS,  $P_{cnmax}$  represents the maximum charging and discharging power of BESS.  $P_{Li}$  and  $E_i$  respectively represent the user load and the rated capacity of the transformer on side i, and  $P_V$  represents the power generated by PV.

#### 3.1.2 PV operation criteria

PV in the system can be regarded as a relatively uncontrollable auxiliary power supply, which can provide a certain power support for the system. Considering the system's economy, PV adopts maximum power point tracking control strategy.

#### 3.1.3 FSOP operation criteria

When distribution network fault occurs, the FSOP operates in  $V_{\rm dc}Q\text{-}Vf$  control mode. At this time, FSOP does not perform active power regulation and only maintains stable power supply on the fault side. In the system overload state, when one transformer overload, the FSOP operates in  $V_{\rm dc}Q\text{-}PQ$  control mode for active power regulation to reduce the load rate of the overload side transformer and improve the system's stability. When two transformers overload, FSOP will not conduct active power regulation.

In the normal operation state, FSOP determines the power value to be regulated according to the power distribution optimization algorithm. The algorithm is based on the equal consumption incremental rate criterion of the transformer.

### 3.1.4 Equal consumption incremental rate criterion of transformer

The two transformers in the system are connected with the distribution network as the main power supply of the system. According to the efficiency characteristics and load rate characteristics of the transformer, the consumption characteristic model of transformers is established. And then, the load distribution of the system is optimized through the equal consumption incremental rate criterion of the transformer to improve the operation efficiency of the transformer. The consumption characteris-tics and power inequality constraints of the two transformers are as follows:

$$\begin{cases} F_{1} = P_{g1} + P_{01} + \left(\frac{P_{g1}}{E_{1}}\right)^{2} P_{k1}, 0 \leq P_{g1} \leq E_{1} \\ F_{2} = P_{g2} + P_{02} + \left(\frac{P_{g2}}{E_{2}}\right)^{2} P_{k2}, 0 \leq P_{g2} \leq E_{2} \end{cases}$$

$$(4)$$

The derivative of the above equation is used to obtain the incremental characteristics  $\lambda_1$  and  $\lambda_2$  of the two transformers, thus establishing the constraint conditions as follows:

$$\begin{cases}

P_{g1} + P_{g1} = T \\

\lambda_1 = \lambda_2

\end{cases}$$

(5)

where  $F_i$ ,  $P_{gi}$ ,  $P_{oi}$ ,  $E_i$  and  $P_{ki}$  are respectively the input power, output power, no-load loss, rated capacity and short circuit current of transformer i. Solve  $F_i$  and  $P_{gi}$  satisfying (4) and (5).

## 3.2 System optimization operation strategy

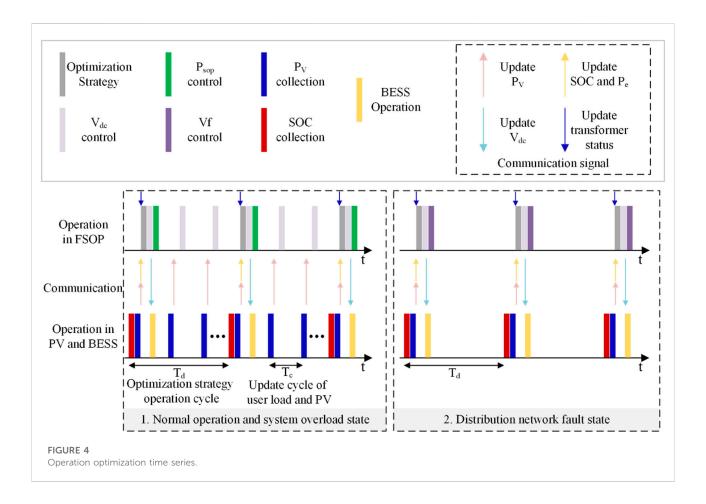

As shown in Figure 2, the system includes three states. In order to realize the stable and economic operation of the system, this paper proposes different operation strategies for different system states, and the optimization time series of system states is shown in Figure 4.

#### 3.2.1 Normal operation state

At the normal operation state, the economic operation of the system is taken as the optimization objective, where the optimization objective can be described as:

$$C = \sum_{t=0}^{t=T} (c(t)P_{in}(t) + cbess \cdot P_{bess})$$

(6)

$$P_{in}(t) = \frac{P_{g1}(t)}{\mu_1(t)} + \frac{P_{g2}(t)}{\mu_2(t)}$$

(7)

where C represents the total electricity costs of the distribution network,  $P_{in}(t)$  and c(t) represent the input power and electricity price of transformers in the period t respectively, cbess represents the electricity cost per kilowatt hour of BESS, and  $P_{bess}$  represents the total charge and discharge of BESS. And  $\mu_i(t)$  means the efficiency of transformer i at time t.

At a certain time, user load, electricity price, and PV output in the system are fixed. Therefore, the system's economy can only be improved by adjusting the charging and discharging power of the BESS and improving the operating efficiency of transformers. To this end, this paper proposes a new optimized operation strategy based on BESS and FSOP. First, FSOP collects signals and determines the charging and discharging power  $P_e$  according to BESS operation criteria and determines the net load of the system at the current time. Then, the output power of the transformers on both sides is determined according to the power distribution optimization algorithm, and then the power value and flow direction on the DC link are determined. Finally, the control signals are generated. The operation optimization time series is shown in Figure 4.

As shown in Figure 4, the optimization strategy operation cycle is  $T_{\rm d}$ , that is, before the next  $T_{\rm d}$ , the control strategy of each converter in the system will not change, and the DC link voltage and the output power of BESS will not change. Only when the next  $T_{\rm d}$  comes, FSOP will collect SOC, the output power of PV and BES. At the same time, FSOP will collect the current load rate of transformers, and then execute optimization strategy to generate new control signals, thereby changing the control strategy of each converter. Among them, BESS operation,  $P_{\rm sop}$  control and  $V_{\rm dc}$  control shown in Figure 4 have been introduced in Section 3.1.

#### 3.2.2 System overload state

At the system overload state, to ensure the safe and stable operation of the system, the operation strategy shall be adjusted to make the transformer operate within the allowable range of rated capacity or reduce its overload. In this state, BESS constantly discharges at the maximum power, and the output control signal  $V_{\rm dc\_value}$  is 850. When one side transformer is overloaded (assuming that the load rate of transformer 2 is higher), FSOP conducts active power regulation to reduce the overload rate of transformer 2. At this time, the output control value  $P_{\rm sop\_value}$  meets (8).

When both transformers are overloaded, FSOP does not conduct active power regulation and only distributes the output power of PV and BESS according to the overload degree of transformers on both sides. First, calculate the power value that needs to be supplemented to the high load rate side when  $\beta 1 = \beta 2$  is met, record the value as  $P_{do}$ , and then distribute the remaining power according to the condition that the load rates on both sides are the same. The output control value  $P_{sop\_value}$  meets (9). The operation optimization time series is shown in Figure 4.

$$P_{sop\_value} = P_e + P_V + E_1 - P_{L1}$$

$$P_{sop\_value} = \begin{cases} P_{do} + \frac{E_2}{E_1 + E_2} (P_e + P_V - P_{do}), & \text{if } P_e + P_V - P_{do} > 0 \\ P_e + P_V, & \text{if } P_e + P_V - P_{do} < 0 \end{cases}$$

(9)

#### 3.2.3 Distribution network fault state

At the distribution network fault state, the system uses the fault isolation function of FSOP to realize uninterrupted power supply of load at the fault side. The FSOP performs  $V_{\rm dc}Q$ -Vf control to maintain the fault side voltage and frequency stability,

and PV and BESS provide power support for the system. The operation optimization time series is shown in Figure 4.

#### 4 Equipment control layer

In the system optimization layer, after FSOP determines the optimization strategy and outputs control signals based on the system state, it is necessary for each unit in the system to work together to realize the economic and stable operation of the system. Since the system involves four converters, in order to transmit the control signal generated by the system optimization to each converter, this paper proposes a control method without a central controller to achieve the coordinated control of each unit in the system.

The operation optimization strategy is implemented in FSOP, so FSOP can directly control both AC/DC converters after outputting control values  $V_{\rm dc\_value}$  and  $P_{\rm sop\_value}.$  However, the converter on the BESS side cannot directly obtain the control signal and needs to be transmitted through the signal path. While PV operates under the maximum power point tracking control strategy, it does not need to be regulated by the control signal of the system optimization layer. Therefore, the controlled quantity is single, and the converter on the BESS side can be controlled by transmitting the control signal through the DC link. PV output is greatly affected by the external environment, BESS operation status switches frequently and capacity is limited, which is not suitable for maintaining DC voltage stability. FSOP can realize the stable control of DC voltage, so FSOP maintains constant DC voltage in this system.

#### 4.1 four-port soft open point control

Control signals  $V_{dc\_value}$  and  $P_{sop\_value}$  generated by the operation optimization strategy determine the control mode of

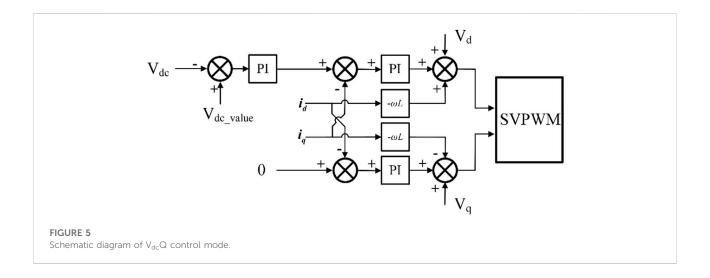

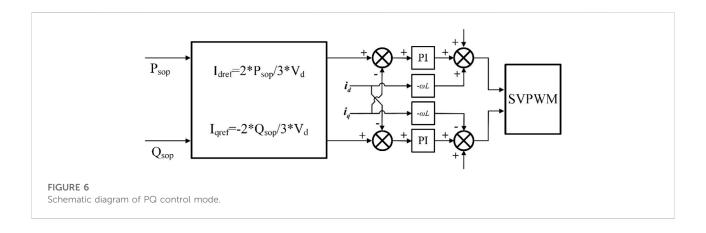

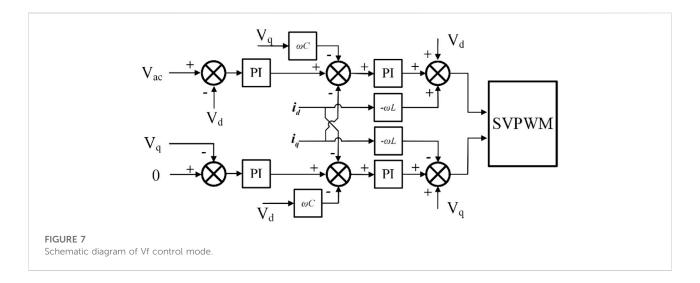

FSOP. One converter operates in V<sub>dc</sub>Q control mode, and the other operates in PQ control mode or Vf control mode (Wang, 2013). As shown in Figure 5, when converter operates in V<sub>dc</sub>Q control mode, V<sub>dc\_value</sub> is input into the control loop as the reference signal of the voltage outer loop, and the DC link voltage is controlled through feedback regulation of the PI controller. As shown in Figure 6, when converter operates in PQ control mode, P<sub>sop\_value</sub> and Q<sub>sop\_value</sub> are input into the control loop as reference signals of the power loop, and the power flow is controlled through negative feedback regulation. When converter operates in Vf control mode, in order to achieve stable power supply of three-phase unbalanced load, the positive sequence, negative sequence and zero sequence voltages are respectively controlled by Vf, and their control block diagrams are shown in Figure 7. When controlling the positive sequence voltage, the reference signal Vac takes the amplitude of the mains voltage 311 V, and when controlling the positive sequence voltage and zero sequence voltage, the reference signal  $V_{ac} = 0$ . At this time, the converter does not need PLL and the value of frequency f is 50 Hz.

### 4.2 Battery energy storage systems control

As mentioned above, the control signal needs to be transmitted to the converter on the BESS side through the DC link. During FSOP operation, the DC link voltage within a certain range can maintain the stable operation of FSOP, so BESS can determine its different operation modes and charge and discharge power values through different DC voltage values. For example, in a 380 V distribution network, DC link voltage in the range of 750VDC ~ 850VDC can maintain the system's stable operation. When the DC link voltage is 780VDC ~820VDC, BESS does not work. When the DC link voltage is

820VDC  $\sim$  850VDC, the BESS is in constant power discharge mode, and the discharge power is (10). When the DC link voltage is 750VDC  $\sim$  780VDC, the BESS is in constant power charging mode, and charging power is (11).

$$P_e = \frac{V_{dc} - 820}{30} P_{cnmax} \tag{10}$$

$$P_e = \frac{V_{dc} - 780}{30} P_{cnmax} \tag{11}$$

#### 5 Simulation results

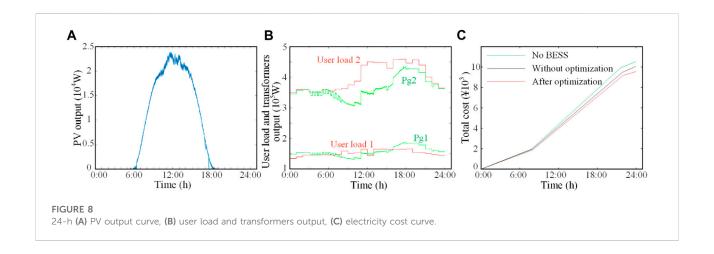

To verify the effectiveness of the optimized operation strategy proposed in this paper, simulation is carried out in Matlab/Simulink. PV output curve measured at Shandong Province is shown in Figure 8A. The peak time, valley time, and electricity price refer to the standards issued by Shandong Province. The electricity price is \0.5769 at 8:00–22:00 and \0.3769 at 0:00–8: 00 and 22:00–24:00. And the transformers used in the simulation

are S9-50/10 and S9-100/10. To simplify the model, this paper does not consider reactive power. Figure 8B shows the actual user load and the output power curve of the transformer after FSOP optimization, and the user load is set according to the average daily power load curve of Shandong Province released in 2018. The red line in the figure indicates the actual user load on both sides of the system, and the green line indicates the output power of transformers after the optimization strategy. The black dashed line indicates the SOC variation curve of BESS.

Figure 8C shows the system electricity cost curve. The PV output and the actual user load are shown in Figure 8A and Figure 8B. The main parameters of BESS are as follows: the maximum capacity is 25 kW h, the maximum power is 7.5 kW, the maximum value of the SOC is 0.9, and the minimum value is 0.2. In Figure 8C, the green line represents the total electricity cost without BESS, the black line represents the total electricity cost without optimization, and the red line represents the total electricity cost after optimization. It can be seen from the figure that the FSOP and its operation strategy proposed in this paper reduce the power consumption cost of the system by about 6%

and 3% respectively compared with the traditional distribution network and FSOP without optimal operation strategy. Therefore, FSOP and its operation optimization strategy can improve the economy of the system.

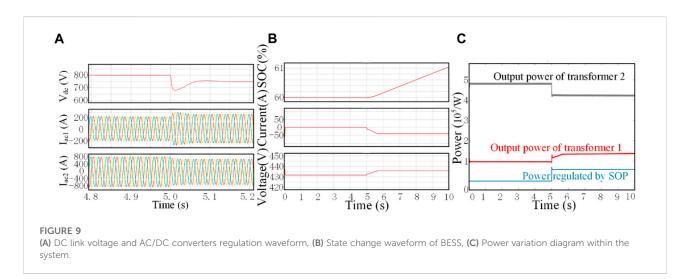

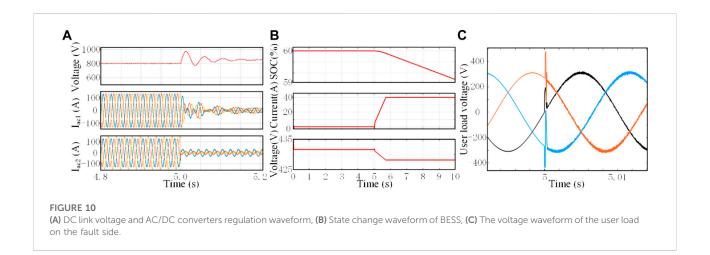

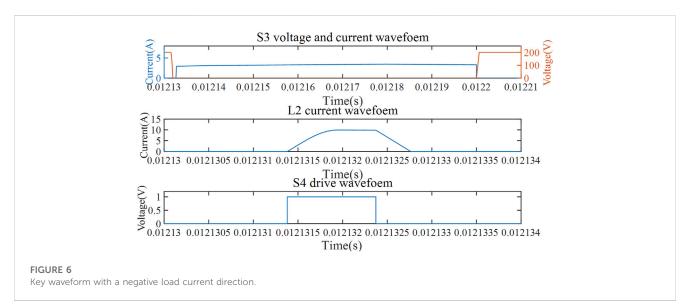

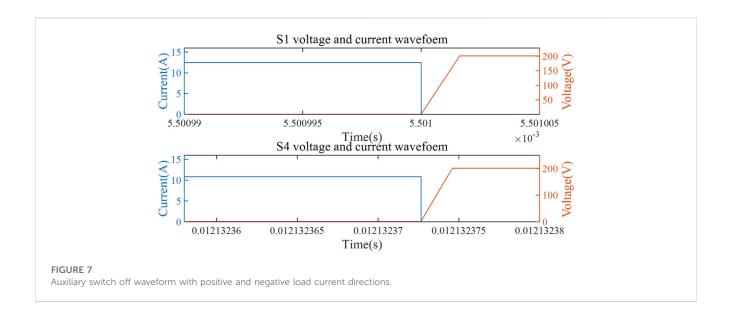

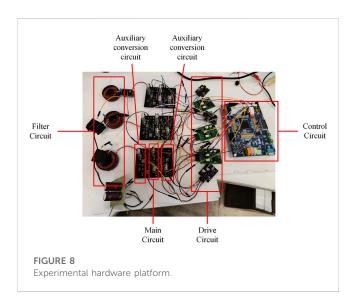

In this paper, the simulation verifies that the converters in the system can achieve cooperative operation under different operating conditions and strategies. Figure 9 shows the waveforms of FSOP, BESS and DC link power when the system generates a new control signal at t = 5 s and the operating state of each port in the system changes. Figure 10 shows the waveforms of the fault-side user load voltage, FSOP, and BESS when the system is switched from the normal operation state to the distribution network fault state. Wherein, Figures 9A, 10A show the DC link voltage, FSOP side converter regulation waveform in 4.8-5.2 s, Figures 9B, 10B shows the waveform of SOC, charging and discharging current, charging and discharging voltage of BESS in  $0\text{--}10\,\text{s}$ . Figure 9C shows the output power value of the system side transformers and the power value regulated through FSOP in 0-10 s. Figure 10C shows the voltage waveform of user load at fault side in case of system fault.

As shown in Figure 9, within  $0 \sim 5$  s, the system does not use the power distribution optimization algorithm for optimal regulation. At this time, the DC link voltage is 800 V, the BESS does not work, and the SOC is constant at 60%. At this time, the output and transfer power of transformers on both sides do not change. When t = 5 s, the system optimization layer uses the power distribution optimization algorithm to adjust and control, generate control signals  $V_{dc\_value}$  and  $P_{sop\_value}$ , where V<sub>dc value</sub> is 750, and P<sub>sop value</sub> is 69,200, and transmit them to each converter. It can be seen from Figure 2 that when t = 5 s, the DC link voltage is rapidly adjusted to 750 V, and the current waveform of converters on both sides of FSOP quickly tends to be stable after a short time adjustment. The BESS changes the charging state and reaches the maximum charging power in about 0.6 s. Part of the load of transformer 2 is transferred to transformer 1 through FSOP to improve the system efficiency.

As shown in Figure 10, when t = 5 s, the system changed from the normal operation state to the distribution network fault state. At this time, the BESS was discharging with the maximum power, and the unbalanced user load on the fault side was quickly restored to power under the control of the FSOP. The simulation results show that the system can realize the cooperative operation of four ports and the stable power supply of unbalanced load on the fault side without central controller.

#### 6 Conclusion

In order to improve the economy and stability of the distribution network, this paper proposes a FSOP and its

optimization strategy and control technology. In this paper, the consumption characteristic model of transformer and the equal consumption incremental rate criterion are established to improve the operation efficiency of transformers. And establish the power distribution optimization algorithm to improve the economy and stability of the system. The system does not need a central controller and only needs DC link voltage to control the equipment in the system.

The optimization strategy proposed in this paper considers only the active load, and the optimization effect is obvious when the load rates of two transformers differ significantly. In future work, the configuration and siting of energy storage capacity for multi-ports SOP will be studied to give full play to the advantages of energy storage and SOP.

#### Data availability statement

The original contributions presented in the study are included in the article/Supplementary Material, further inquiries can be directed to the corresponding author.

#### **Author contributions**

XZ is the main author of the paper and experiment. XG and XZ provide technical support and suggestions, and assist in completing papers and experiments, and help XZ collect data. FG guides XZ to complete the experiment and paper writing, and provides theoretical support.

#### Conflict of interest

Authors XG and XZ were employed by Yangzhou Huading Electric Co., Ltd.

The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

#### Publisher's note

All claims expressed in this article are solely those of the authors and do not necessarily represent those of their affiliated organizations, or those of the publisher, the editors and the reviewers. Any product that may be evaluated in this article, or claim that may be made by its manufacturer, is not guaranteed or endorsed by the publisher.

#### References

Bloemink, Jeffrey M., Timothy, C., and Green, P. (2013). Benefits of distribution-level power electronics for supporting distributed generation growth. *IEEE Trans. Power Deliv.* 28 (2), 911–919. doi:10.1109/tpwrd.2012. 2232313

Bloemink, J. M., and Green, T. C, P. (2013). Benefits of distribution-level power electronics for supporting distributed generation growth. *IEEE Trans. Power Deliv.* 28 (2), 911–919. doi:10.1109/tpwrd.2012.2232313

Cao, W., Wu, J., Jenkins, N., Wang, C., and Green, T. (2016). Benefits analysis of soft open points for electrical distribution network operation. *Appl. Energy* 165, 36–47. doi:10.1016/j.apenergy.2015.12.022

Chen, H., Xia, F., Yuan, D., Liu, Y., Chen, L., Qin, X., et al. (2020). Optimal configuration scheme of fast electric vehicle charging station with photovoltaic in DC distribution network. *Automation Electr. Power Syst.* 44 (16), 53–60. doi:10.7500/AEPS.2010.12005

Conti, S., Nicolosi, R., Rizzo, S. A., and Zeineldin, H. H. (2012). Optimal dispatching of distributed generators and storage systems for MV islanded microgrids. *IEEE Trans. Power Deliv.* 27 (3), 1243–1251. doi:10.1109/tpwrd.2012.2194514

Ding, M., Zhang, Y., Mao, M., Liu, X., and Xu, N. (2011). Economic operation optimization for microgrids including Na/S battery storage. *Proc. CSEE* 31 (4), 7–14.

Haoran, J., Wang, C., Li, P., Ding, F., and Wu, J. (2019). Robust operation of soft open points in active distribution networks with high penetration of photovoltaic integration. *IEEE Trans. Sustain. Energy* 10 (1), 280–289. doi:10.1109/tste.2018.2833545

Huang, S., Wu, Q., Oren, S. S., Li, R., and Liu, Z. (2015). Distribution locational marginal pricing through quadratic programming for congestion management in distribution networks. *IEEE Trans. Power Syst.* 30 (4), 2170–2178. doi:10.1109/tpwrs.2014.2359977

Huang, W., Wu, P., Tai, N. L., Ma, Z. J., Yang, L. Q., Zhang, E. J., et al. (2019). Architecture design and control method for flexible connected multiple microgrids based on hybrid unit of common coupling. *Proc. CSEE* 29 (12), 3499–3513. doi:10. 13334/j.0258-8013.pcsee.172163

Kashani, M. G., Mobarrez, M., and Bhattacharya, S., P. (2019). Smart inverter volt-watt control design in high PV-penetrated distribution systems. *IEEE Trans. Ind. Appl.* 55 (2), 1147–1156. doi:10.1109/tia.2018.2878844

Li, Z., Zhang, F., Liang, J., Yun, Z., and Zhang, J. (2015). Optimization on microgrid with combined heat and power system. *Proc. CSEE* 35 (14), 3569–3576. doi:10.13334/j.0258-8013.pcsee.2015.14.011

Li, Z., Ye, Y., Wang, Z., Wu, Y., and Xu, H. (2021). Integrated planning and operation evaluation of micro-distribution network based on flexible multi-state switch interconnection. *Trans. China Electrotech. Soc.* 36 (2), 487–495. doi:10.19595/j.cnki.1000-6753.tces.J90174

Miu, Y., Cheng, H., Gong, X., Wang, L., Yao, L., and Masoud, B. (2012). Evaluation of a distribution network connection mode considering micro-grid. *Proc. CSEE* 32 (1), 17–23. doi:10.13334/j.0258-8013.pcsee.2012.01.008

Rueda-Medina, A. C., and Padilha Feltrin, A. P. (2013). Distributed generators as providers of reactive power support-a market approach. *IEEE Trans. Power Syst.* 28 (1), 490–502. doi:10.1109/tpwrs.2012.2202926

Verzijlbergh, R., De-Vries, L., and Lukszo, Z. P. (2014). Renewable energy sources and responsive demand. Do we need congestion management in the distribution grid. *IEEE Trans. Power Syst.* 29 (5), 2119–2128. doi:10.1109/tpwrs.2014.2300941

Wang, C., Song, G., Li, P., Zhao, J., Wu, J., et al. (2016a). A hybrid optimization method for distribution network operation with SNOP and tie switch. *Proc. CSEE* 36 (9), 2315–2321. doi:10.13334/j.0258-8013.pcsee.2016.09.001

Wang, C., Song, G., Li, P., Ji, H., Zhao, J., and Wu, J. (2017). Optimal configuration of soft open point for active distribution network considering the characteristics of distributed generation. *Proc. CSEE* 37 (7), 1889–1896. doi:10.13334/j.0258-8013.pcsec.152649

Wang, C., Song, G., Li, P., Yu, H., Zhao, J., Wu, J., et al. (2016b). Research and prospect for soft open point based flexible interconnection technology for Smart distribution network. *Automation Electr. Power Syst.* 40 (22), 168–175. doi:10.7500/

Wang, C., Sun, C., Peng, K., Li, Y., Wu, Z., et al. (2013). Study on AC-DC hybrid power flow algorithm for microgrid. *Proc. CSEE* 33 (4), 8–15. doi:10.13334/j.0258-8013.pcsee.2013.04.007

Wang, C., Ji, J., Ji, H., Yu, H., Wu, J., and Li, P. (2022). Technologies and application of soft open points in distribution networks. *Automation Electr. Power Syst.* 46 (4), 1–14. doi:10.7500/AEPS20210514005

Wang, J., Zhou, N., Chung, C. Y., and Wang, Q. (2020). Coordinated planning of converter-based DG units and soft open points incorporating active management in unbalanced distribution networks. *IEEE Trans. Sustain. Energy* 11 (3), 2015–2027. doi:10.1109/tste.2019.2950168

Xue, F., Ma, L., Zhu, H., Shi, J., and Qiao, W. (2020). Bi-level programming of distributed generations in flexible distribution network with SOP optimization. *Proceeding CSU-EPSA* 32 (8), 109–115. doi:10.19635/j.cnki.csu-epsa.000302

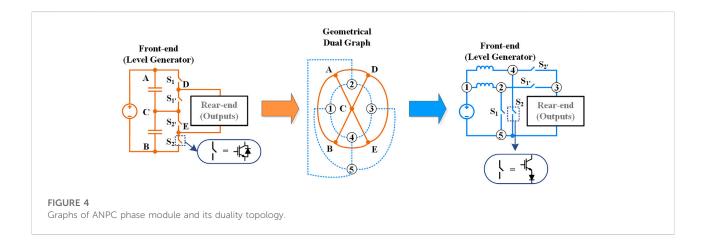

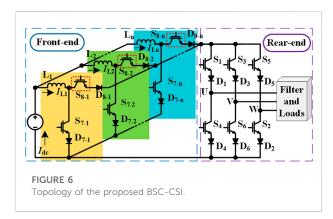

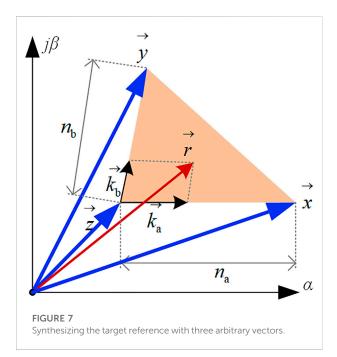

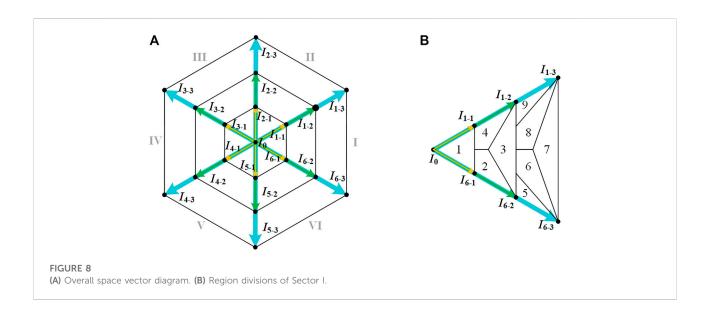

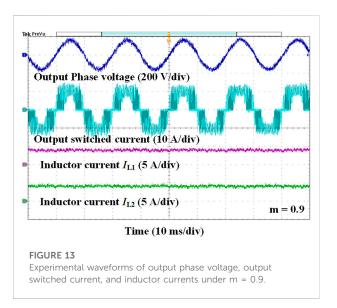

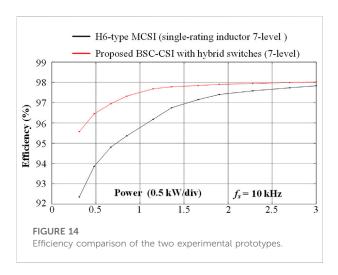

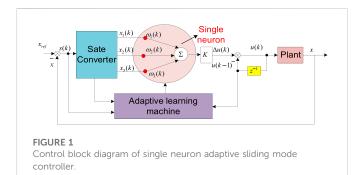

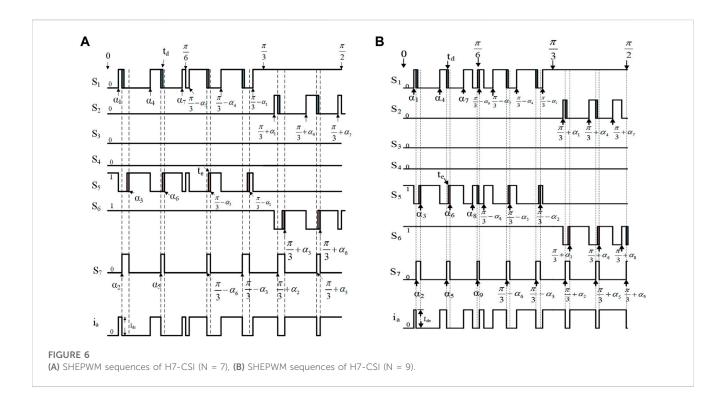

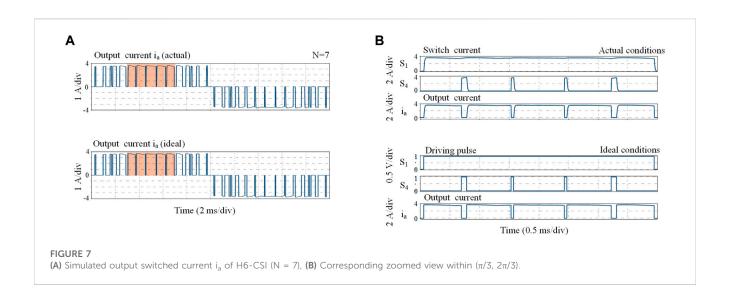

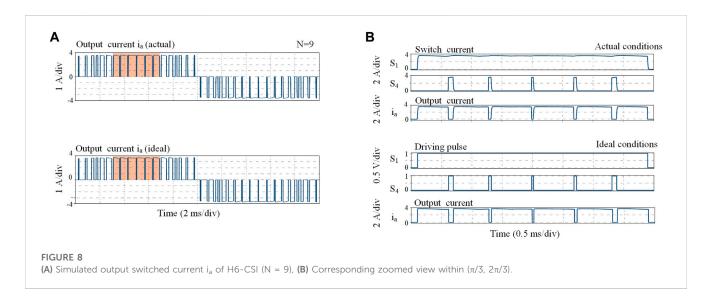

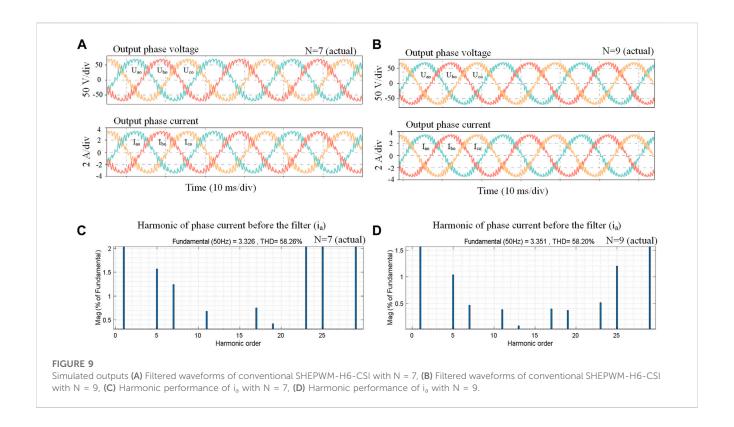

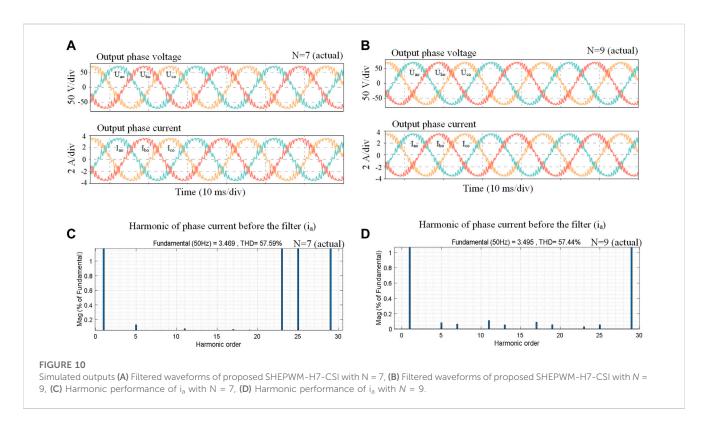

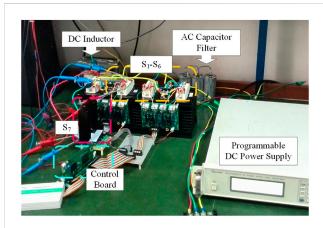

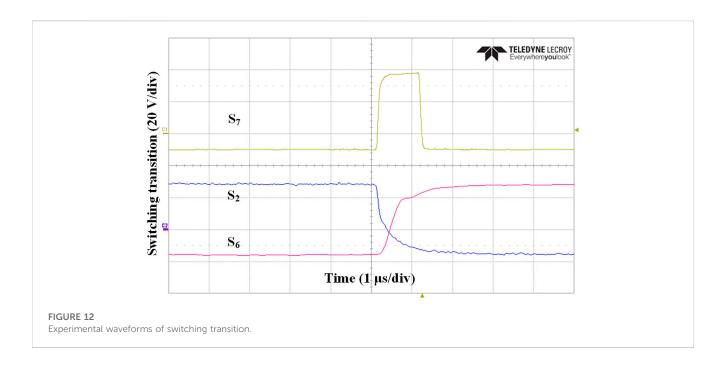

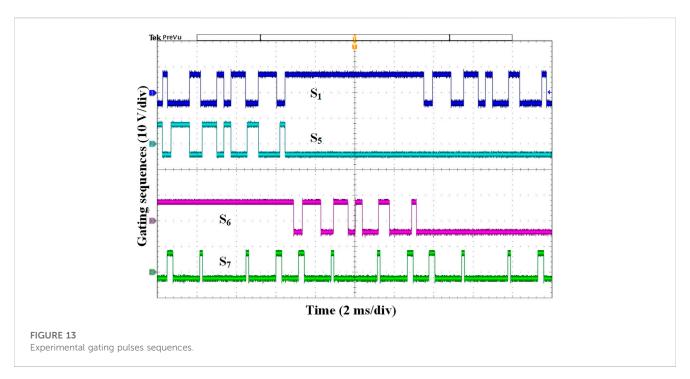

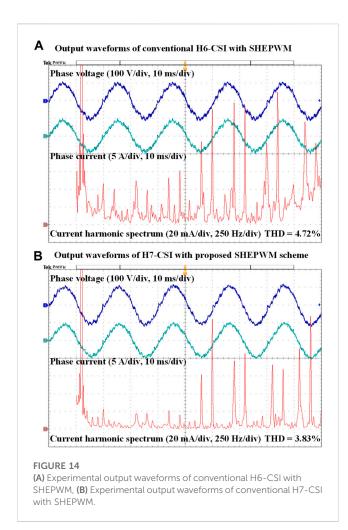

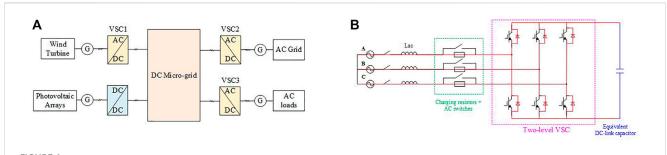

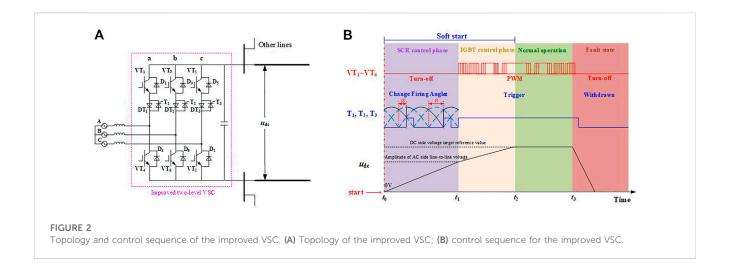

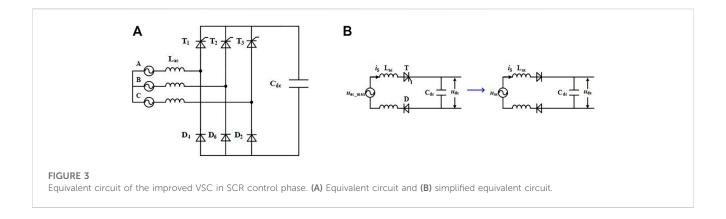

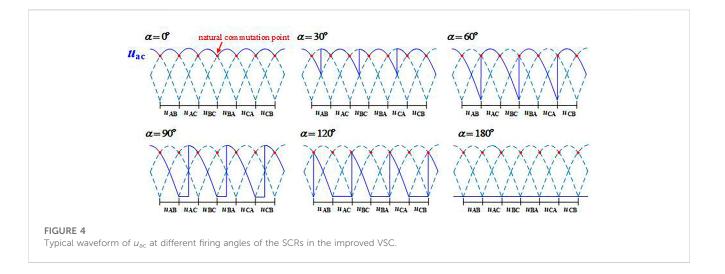

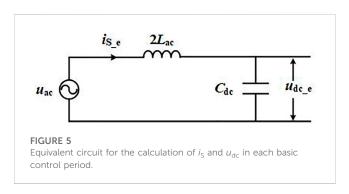

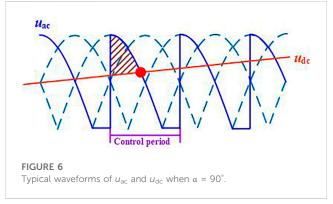

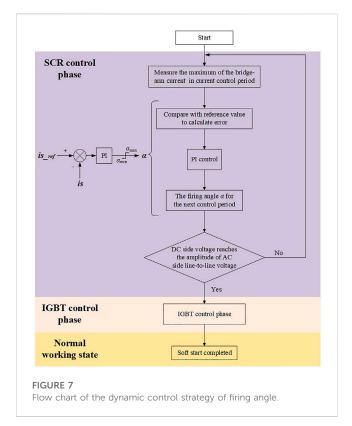

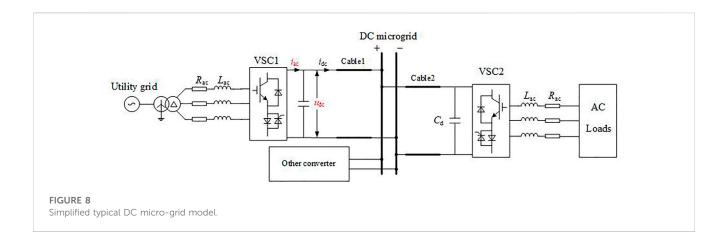

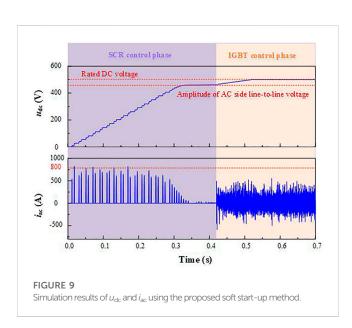

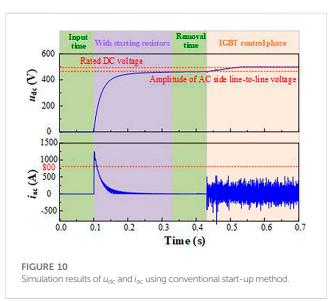

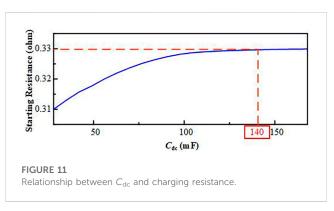

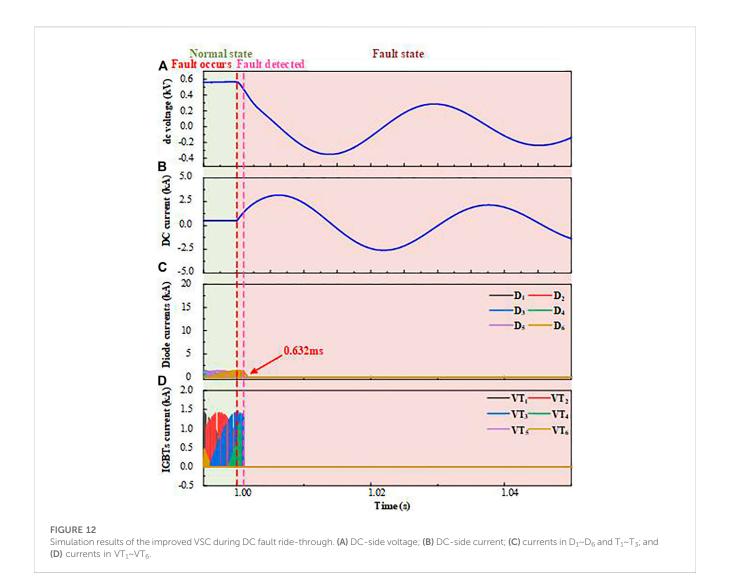

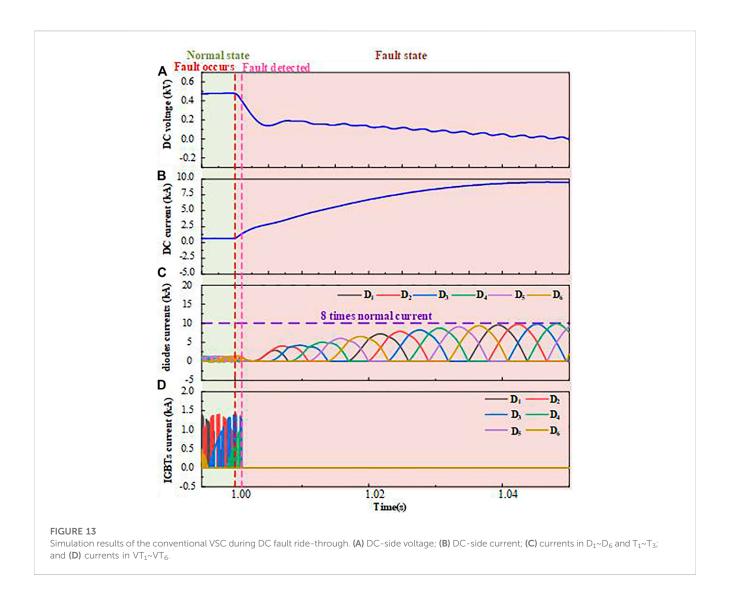

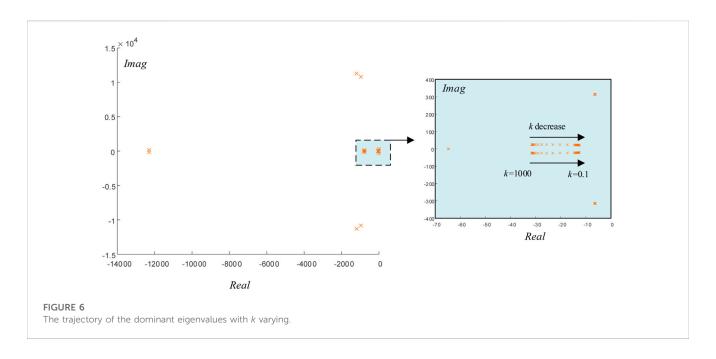

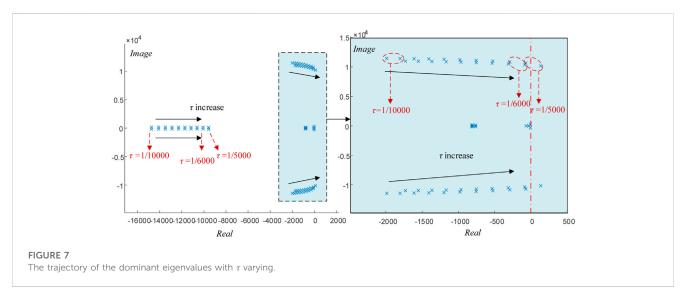

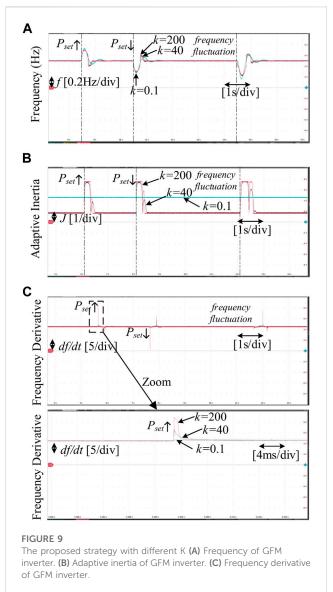

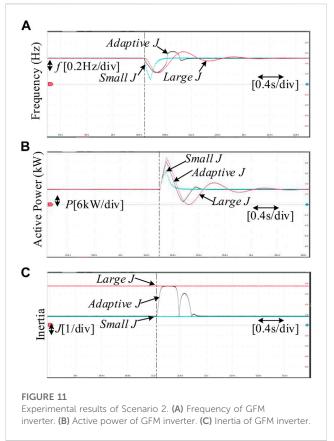

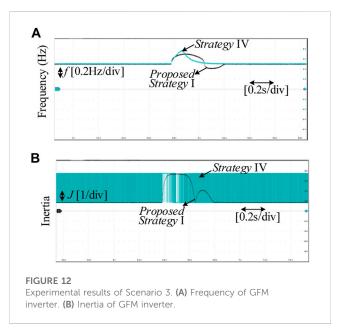

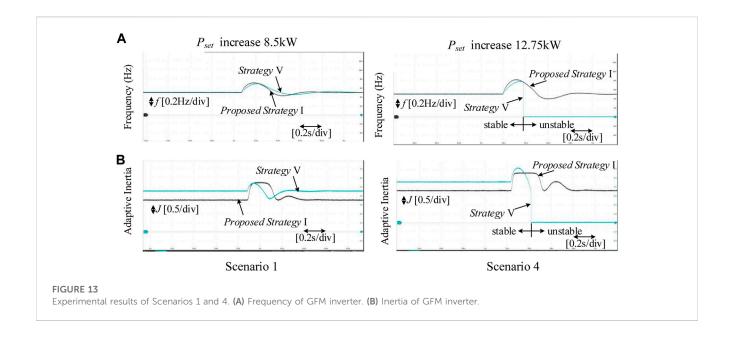

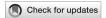

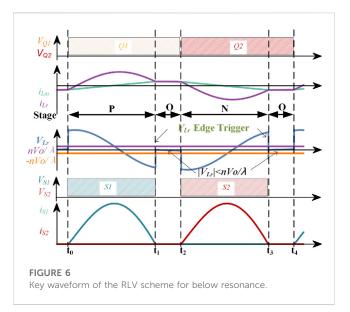

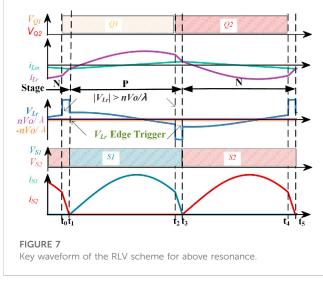

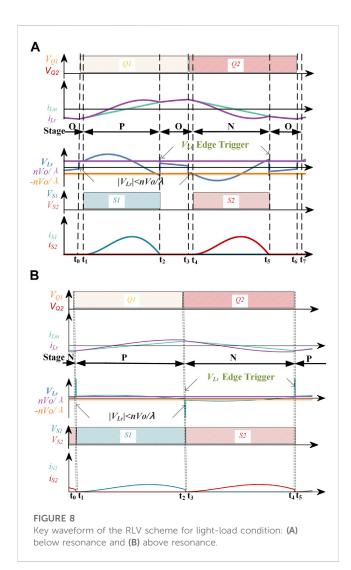

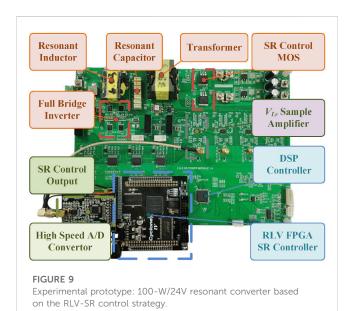

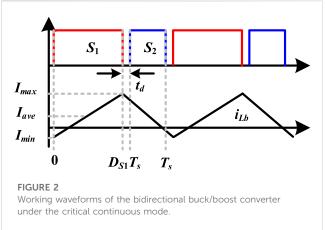

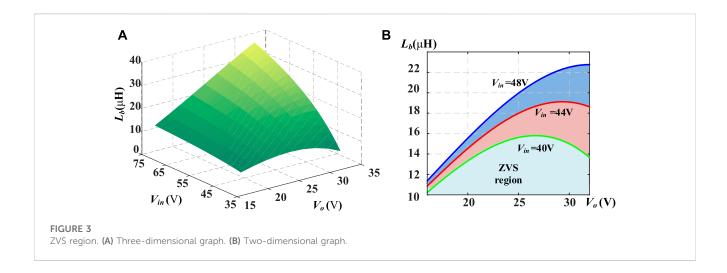

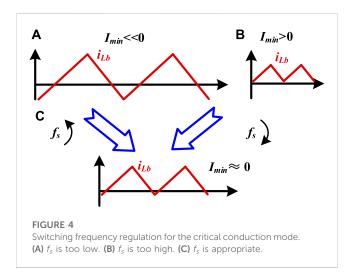

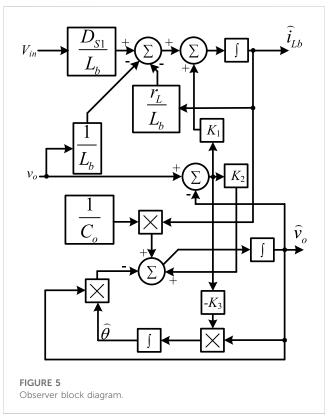

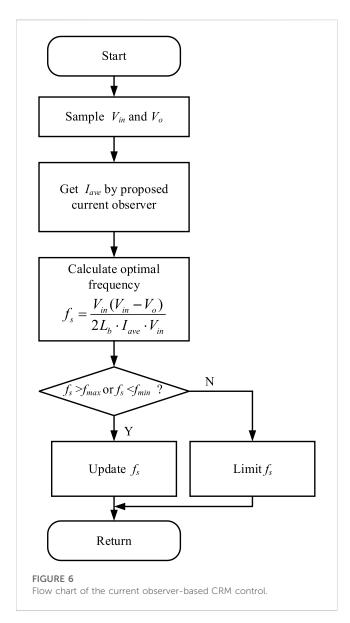

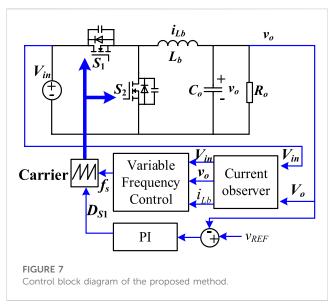

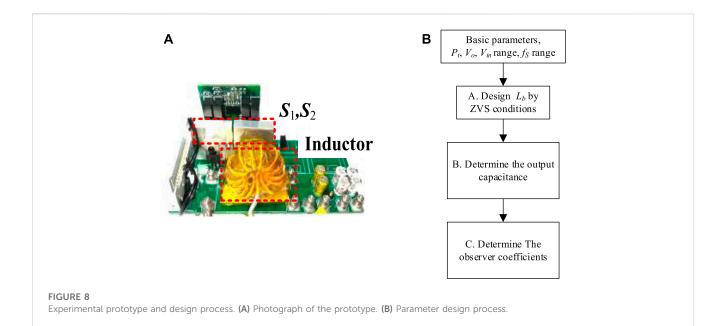

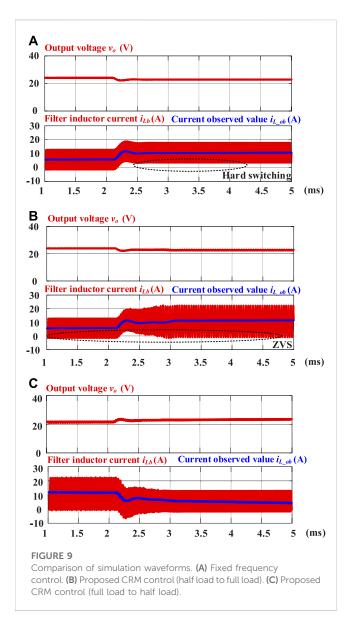

Wu, P., Huang, W., Tai, N., Lu, Y., Ni, C., and Zong, M. (2019). Multi-layer coordinated control strategy for island operation of flexible interconnected multi microgrid based on power mutual assistance. *High. Volt. Eng.* 45 (10), 3101–3111. doi:10.13336/j.1003-6520.hve.20190924009