- 1National Space Science Center, The Chinese Academy of Sciences, Beijing, China

- 2University of Chinese Academy of Sciences, Beijing, China

This paper conducts a comprehensive survey and analysis of interconnection buses for space applications both domestically and internationally in recent years. In response to the future demands of satellites for high-performance computing, high-efficiency data processing, and high-speed data transmission in space missions, it proposes the integration of TSN (Time-Sensitive Networking) and RDMA (Remote Direct Memory Access) as a novel bus architecture for aerospace systems. The study investigates the developmental trajectory, practical implementations, and future prospects of TSN technology, alongside a parallel examination of RDMA’s evolution, deployments, and emerging trends. Synthesizing these findings, the paper presents a forward-looking perspective on space applications leveraging the TSN+RDMA high-performance interconnection bus.

1 Introduction

With the development of satellite applications towards intelligence, high real-time performance, and multifunctional collaboration (such as on-board AI processing, high-resolution remote sensing real-time transmission, constellation collaborative networking), the problems of low bandwidth (usually<1 Gbps), high latency (μs∼ms level), and poor scalability of traditional satellite buses (such as SpaceWire, CAN) are becoming increasingly prominent. For example, the data rate of modern remote sensing satellite payloads has exceeded 40 Gbps, while the existing bus bandwidth still remains at several hundred Mbps, forming a serious “transmission bottleneck”. At the same time, high-performance ground interconnect technologies such as TSN, RDMA, PCIe have achieved Tbps level bandwidth and ns level latency in data centers, but their adaptability research in space environments (radiation, temperature difference, vibration) is almost blank. How to integrate and optimize the deterministic scheduling of TSN, the low overhead transmission of RDMA, and the high bandwidth characteristics of PCIe into an interconnect architecture suitable for aerospace scenarios has become a key issue that urgently needs to be overcome.

Current spacecraft electronic systems are undergoing a profound transformation, evolving toward distributed, modular architectures with high reliability and hard real-time capabilities. On one hand, the widespread adoption of advanced high-performance computing units, high-capacity storage arrays, and heterogeneous smart payloads based on commercial/industrial-grade components demands an interconnection neural hub featuring ultra-high throughput, ultra-low deterministic latency, flexible topological support, and robust quality-of-service (QoS) guarantees. On the other hand, missions such as deep-space exploration and constellation networking impose stringent requirements for long-term orbital reliability, autonomous management, and fault tolerance, necessitating critical subsystems with exceptional bus robustness, fault-tolerant mechanisms, and maintainability. Though emerging technologies like SpaceFibre achieve bandwidth improvements (up to 6.25 Gbps), substantial theoretical and generational gaps persist in fulfilling future aerospace requirements: terabit-level aggregated bandwidth, nanosecond-scale deterministic latency, dynamically reconfigurable topologies, and intelligent multi-fault self-healing capabilities in space environments. Furthermore, core technologies including high-speed Serializer/Deserializer (SerDes) IP and radiation-hardened protocol controllers face indigenous R&D barriers, constraining China’s development of a comprehensive high-performance on-board bus ecosystem.

This research focuses on innovating architectures and tackling core technologies for next-generation high-performance on-board interconnection buses, aiming to break through traditional bottlenecks and construct a core information transmission infrastructure supporting future aerospace mission requirements. The study centers on three key dimensions: unifying ultra-high throughput with deterministic latency, intelligent survivability and autonomous reconfiguration, and multi-dimensional integrated reliability assurance. Specifically, it explores ultra-high-speed transmission pathways leveraging novel physical-layer mechanisms such as optical/electrical integration and spatial division multiplexing; designs protocol stacks with nanosecond-scale temporal determinism and intelligent traffic shaping capabilities; constructs intelligent switching cores supporting dynamic topological reconfiguration and multi-path redundancy; and pioneers end-to-end space-hardened transmission mechanisms incorporating hardware acceleration (e.g., adaptive forward error correction, single-event upset (SEU) hardening, and link-level fast switching). Through systematic innovation, this research is expected to achieve generational leaps in transmission bandwidth, real-time performance, reliability, and flexibility, thereby bridging critical technological gaps in China’s capabilities for ultra-high-speed, highly reliable, and intelligent on-board interconnection systems.

Current research predominantly focuses on optimizing single technologies, lacking systematic exploration of multi-protocol synergy and space adaptability. For instance, existing TSN (Time-Sensitive Networking) studies neglect radiation-induced clock synchronization drift, while the reliability of RDMA (Remote Direct Memory Access) protocols under space single-event effects (SEEs) remains unverified. Through convergent innovation and interdisciplinary approaches (aerospace electronics + high-speed communication + real-time systems), this study aims to break through the performance limits of traditional buses and advance indigenous and controllable development of China’s on-board interconnection technologies.

2 Current status of on-board interconnection buses

2.1 Overall

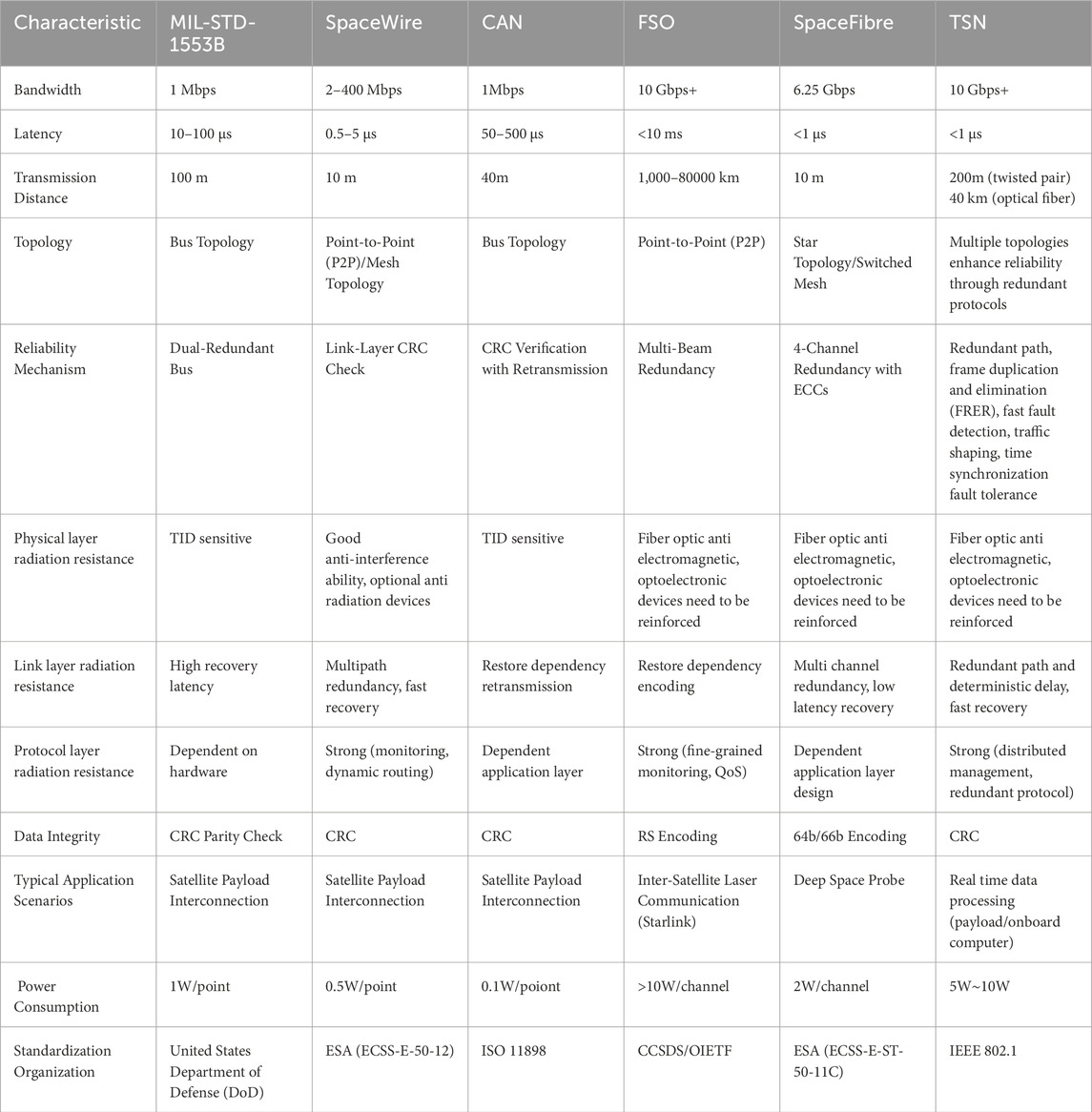

Current spatial interconnection bus technologies are advancing rapidly both domestically and internationally, aiming to enhance communication efficiency and reliability within spacecraft and between spacecraft systems. As a core enabler for space information networks and spacecraft interconnectivity, spatial buses play a pivotal role in modern aerospace architectures. Globally, multiple bus standards have been widely adopted in spacecraft, including MIL-STD-1553B, SpaceWire, CAN (Controller Area Network), FSO (Free-Space Optical), and SpaceFibre, with their key parameters compared in Table 1 below.

2.2 Space application of 1553B bus

MIL-STD-1553B bus is widely used in the aerospace field due to its high reliability, including satellite communications, spacecraft navigation and control, as well as data acquisition and transmission (Jiang et al., 2020; Lan et al., 2021).

Within satellites, the MIL-STD-1553B bus is commonly deployed as a control bus to coordinate operations among internal components and facilitate communication between the satellite and ground stations (Jiang et al., 2020).

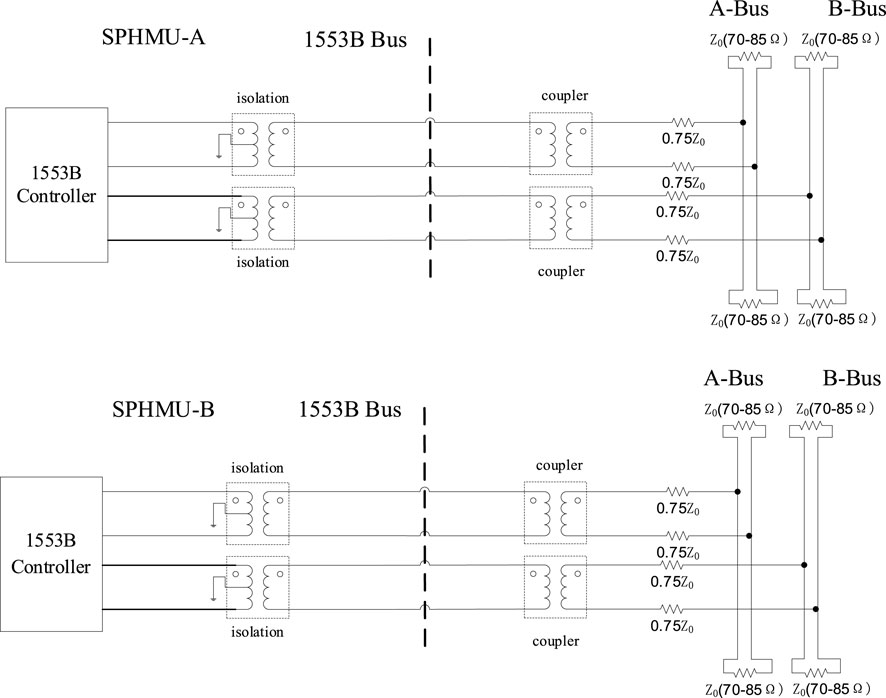

With the widespread application of the 1553B bus in the aerospace field, demands for reliability have become increasingly stringent. However, the information transmission bottleneck of the 1553B bus lies in the Bus Controller (BC). Therefore, it is necessary to develop a fault-tolerant 1553B bus controller (Dong-wei et al., 2012). The complex 1553B Bus construction standards is shown in Figure 1.

Although the MIL-STD-1553B bus has been widely used in the aerospace field for decades, it faces emerging challenges with technological advancements. For instance, to address increasing demands for communication bandwidth, novel technologies are being explored to replace or enhance the functionality of the 1553B bus (Mifdaoui et al., 2007). Full-duplex switched Ethernet is recognized as an attractive alternative to overcome the limitations of the MIL-STD-1553B data bus (Mifdaoui et al., 2007). Furthermore, optical wireless communication (OWC) transceivers are under development for transmitting MIL-STD-1553B signals, thereby reducing extensive wiring on spacecraft (Cossu et al., 2022). As spacecraft increasingly interface with external systems or networks, cybersecurity risks have become critical (He et al., 2019). Consequently, intrusion detection systems are essential to protect MIL-STD-1553-based systems from cyber attacks (He et al., 2019). An anomaly detection method based on sparse autoencoder (SAE) and integrated Mahalanobis distance (IMD) has been proposed to identify remote terminal (RT) spoofing attacks on the MIL-STD-1553B data bus, preventing integrated avionics systems (IAS) from network paralysis due to false judgments (Stan et al., 2020).

2.3 Space application of CAN bus

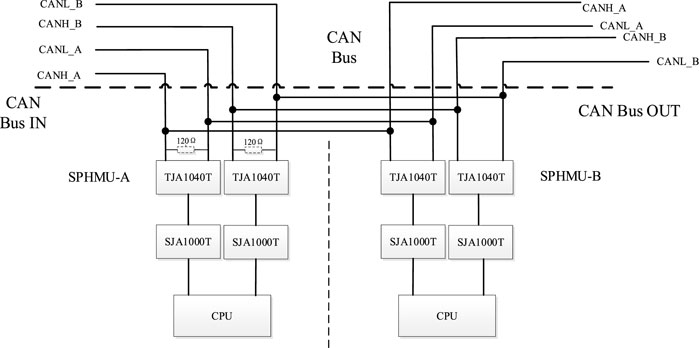

Due to its reliability, real-time performance, and anti-interference capability, the CAN bus has been applied in the aerospace field, particularly in distributed control systems of satellites and spacecraft (Seoane et al., 2021). The complex CAN Bus construction standards is shown in Figure 2.

CAN bus exhibits the following advantages in space applications:

High Reliability: CAN bus features error detection and correction capabilities, ensuring reliable data transmission (Sen, 2021). Additionally, system reliability can be further enhanced through redundant design (Chen et al., 2008).

Real-Time Performance: The priority-based arbitration mechanism of CAN bus guarantees real-time transmission of critical data (Sen, 2021; Zheng et al., 2011).

Anti-Interference Capability: Differential signaling employed by CAN bus provides robust immunity to common-mode interference (Seoane et al., 2021).

Flexibility: As a multi-master bus, CAN enables flexible construction of distributed control systems (Han et al., 2023; Yang et al., 2020).

Standardization: The European Space Agency (ESA) has established the ECSS-E-ST-50-12C CAN bus standard, providing specifications for CAN bus applications in the aerospace domain (Seoane et al., 2021).

2.4 Space application of spacewire bus

SpaceWire is a serial communication protocol designed for space applications, providing high-speed and reliable data transmission (Levchenko et al., 2018). Originally developed by the European Space Agency (ESA), it facilitates data exchange between internal subsystems of spacecraft. SpaceWire exhibits the following characteristics:

High-Speed Data Transfer: Supports data rates up to 400 Mbps, meeting the requirements of numerous space applications (Levchenko et al., 2018).

Simplified Protocol: Relatively simple implementation reduces hardware and software development complexity.

Flexible Topology: Accommodates point-to-point, star, and mesh configurations, enabling flexible construction of complex communication networks.

Fault Tolerance: Ensures data reliability through link-level retransmission and error detection mechanisms.

2.5 Space application of FSO bus

Free Space Optical Communication (FSO) is a technology that utilizes the atmosphere or vacuum as a transmission medium to transfer data via optical signals. Compared to traditional radio frequency (RF) communication, FSO offers the following advantages (Behbahani et al., 2020):

High Bandwidth: FSO provides extremely high bandwidth, meeting the growing demands for data transmission.

Security: The directional nature of laser beams makes eavesdropping difficult, resulting in enhanced security.

No Spectrum License Required: FSO operates in the optical band, eliminating the need for radio spectrum licensing.

However, FSO faces several challenges:

Atmospheric Effects: When transmitting through the atmosphere, optical signals are susceptible to weather conditions (e.g., fog, rain, snow), leading to signal attenuation.

Alignment Requirements: Precise beam alignment is necessary to ensure communication quality.

Distance Limitations: Transmission distance is constrained due to optical signal attenuation.

2.6 Space application of SpaceFibre bus

SpaceFibre bus demonstrates broad application prospects in the aerospace domain, particularly in high data-rate transmission, electromagnetic interference immunity, and simplified data bus architecture.

Compared to traditional metal cables, optical fiber buses exhibit the following significant advantages, making them ideal for space applications:

Light Weight: Optical fibers are lighter than copper wires, which is critical in weight-sensitive aerospace applications (Taylor and Thacker, 1982).

High Bandwidth: Optical fibers support extremely high data transmission rates, meeting the increasing data demands of spacecraft (Taylor and Thacker, 1982; Zheng et al., 2022; Nannipieri et al., 2020). SpaceFibre achieves data rates of 6.25 Gbps per channel and supports multi-channel aggregation.

Electromagnetic Interference (EMI) Immunity: Optical fibers are immune to electromagnetic interference, ensuring data transmission reliability—especially crucial in complex spacecraft electromagnetic environments (Taylor and Thacker, 1982; Behbahani et al., 2020).

Simplified Data Bus Architecture: The use of optical fibers simplifies data bus architecture, reducing complexity and cost (Taylor and Thacker, 1982).

2.7 Conclusion

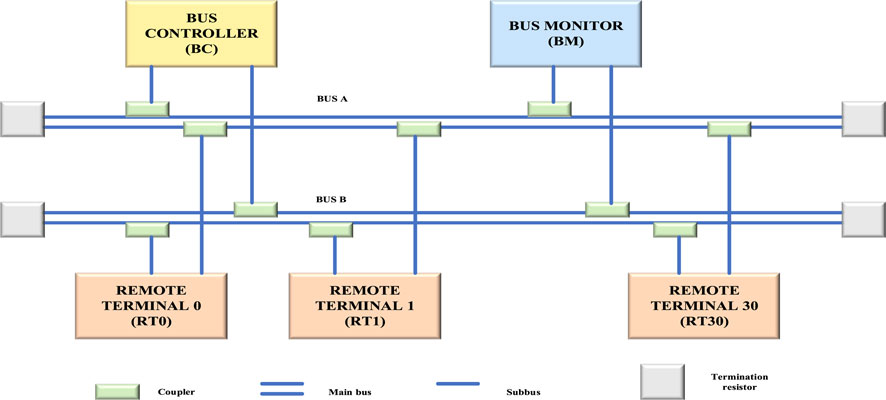

The MIL-STD-1553B bus excels in maturity and reliability, with its dual-redundant bus design adapted for high-safety scenarios such as rocket control, but is constrained by low bandwidth (1 Mbps) that cannot support high-resolution remote sensing data transmission, as shown in Figure 3;

SpaceWire bus offers low-latency dynamic routing, ideal for interconnecting multiple payloads within satellites (e.g., ESA’s Mars Express), yet lacks native redundancy and relies on upper-layer protocols for fault tolerance;

CAN bus leverages multi-master contention and low-cost deployment for in-vehicle sensor networks, but its bandwidth (≤1 Mbps) and distance limitations (40 m at 1 Mbps) render it unsuitable for high-speed data transfer;

FSO (Free Space Optical Communication) achieves ultra-high rates (>10 Gbps) and EMI immunity, resolving inter-satellite “bandwidth wall” issues, yet faces challenges including complex ATP (Acquisition, Tracking, Pointing) systems, atmospheric turbulence degrading ground links, and point-to-point limitations preventing multi-device networking;

SpaceFibre bus, as an upgraded version of SpaceWire, introduces breakthroughs such as multi-channel parallel transmission (aggregate bandwidth: 4 × 6.25 Gbps = 25 Gbps), coexistence of control flows (highest priority) with scientific data streams, and backward compatibility with SpaceWire.

3 Current development status of TSN interconnect bus

3.1 History of TSN

During the period from the 1980s to 2005, traditional Ethernet relied on a Best Effort transmission mechanism, characterized by high latency jitter and an inability to guarantee real-time performance, making it unsuitable for industrial control requirements (Xia et al., 2022).

During the period from 2005 to 2012, the IEEE 802.1 working group established the Audio Video Bridging (AVB) Task Group to address professional audio/video transmission requirements, resolving high-bandwidth and low-latency synchronization challenges (e.g., live performances and broadcast centers). Core technologies included Time Synchronization (IEEE 802.1AS) and Traffic Shaping (IEEE 802.1Qav), which laid the foundation for subsequent TSN standards.

As real-time critical systems advanced, traditional communication networks failed to meet demands for high bandwidth and low latency. Although Audio Video Bridging (AVB) was developed in 2005, it lacked fault tolerance and security mechanisms. Time-Sensitive Networking (TSN) evolved from AVB in 2012, introducing enhanced features such as improved time synchronization, redundancy functions, and stream filtering.

The core characteristic of TSN is its Time-Triggered Paradigm based on globally synchronized offline scheduling tables. When a Time-Triggered (TT) message is ready while a Rate-Constrained (RC) message is already in transmission, three integration methods—Preemption, mmediate Blocking, and Reordering—are employed to resolve conflicts. Beyond several real-time Ethernet solutions, Time-Sensitive Networking (TSN) also exhibits significant interest and appeal in meeting the growing variable transmission demands of the automotive and aerospace industries. TSN comprises several IEEE standards developed by the IEEE 802.1 TSN Task Group, such as 802.1AS, 802.1Qav, 802.1Qat, 802.1BA, 802.1Qbv, and 802.1Qbu (Chen et al., 2024; Zanbouri et al., 2024).

On top of the Static Priority Queuing (SPQ) scheduling mechanism, TSN introduces guaranteed timing behavior while concurrently processing Best-Effort traffic. It specifically focuses on:

Control Data Traffic (CDT) transmission under the Time-Aware Shaper (TAS, IEEE 802.1Qbv);

Audio-Video stream transmission under the Credit-Based Shaper (CBS, IEEE 802.1Qav);

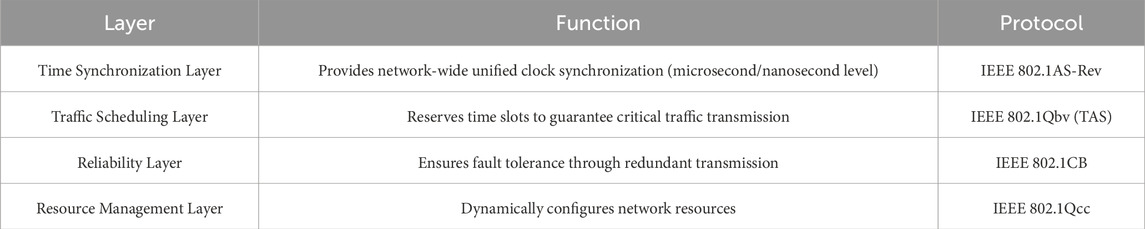

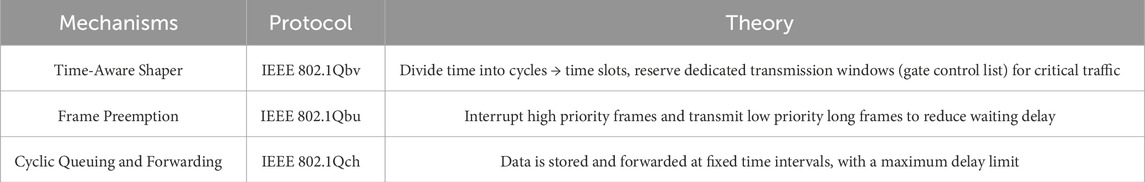

TSN achieves deterministic communication through a layered model. The hierarchical architecture is detailed in Table 2, and deterministic mechanisms are summarized in Table 3.

3.2 Applications of TSN in industry

TSN technology has received widespread attention both domestically and internationally, and has made significant progress in fields such as industrial automation and automotive systems.

Domestic enterprises actively explore the application of TSN in industrial Internet and intelligent manufacturing (Zhang et al., 2024). For example, some enterprises are developing industrial Ethernet solutions based on TSN to meet the real-time, reliability, and synchronization requirements of industrial control systems (Chen et al., 2024; Jin et al., 2024).

The China Academy of Information and Communications Technology and other institutions actively participate in the development and promotion of TSN related standards. This will help promote the standardization and standardized application of TSN technology in China.

Domestic enterprises including Huawei, Hikvision, ZTE, etc. have made certain progress in the development and implementation of TSN solutions in industrial environments. These enterprises are committed to applying TSN technology to their own business areas to enhance the competitiveness of their products and solutions.

The IEEE TSN working group abroad is committed to developing TSN related standards to ensure interoperability between devices from different vendors Chahed and Kassler, 2023; Deng et al., 2022; Fejes et al., 2022; Jiang et al., 2023). These standards cover key technologies such as time synchronization (Wang et al., 2024), traffic scheduling, and reliability assurance.

TSN technology has been widely applied in industrial automation, automotive electronics, aerospace and other fields abroad (Fangmin et al., 2020; Zhang et al., 2024; Vinaya, 2025; Bruckner et al., 2019). For example, in the automotive field, TSN is used to achieve real-time communication inside the car, supporting advanced driver assistance systems (ADAS) and autonomous driving functions (Deng et al., 2022). Automobile manufacturers such as BMW and industrial giants such as Siemens actively participate in the research and application of TSN technology. These enterprises apply TSN technology to their products and solutions to enhance their performance and reliability. A large number of research institutions and universities are also conducting TSN related research work, involving scheduling algorithms, network optimization, security, and other aspects (Vinaya, 2025; Bruckner et al., 2019). These research results provide theoretical support and technical reserves for the further development of TSN technology.

3.3 Potential Applications of TSN in aerospace

Time-Sensitive Networking (TSN) technology is increasingly regarded as a critical communication infrastructure in future aerospace systems, particularly for aerospace applications with stringent requirements on real-time performance, reliability, and security. By providing deterministic data transmission, TSN meets the growing demands of the aerospace domain for communication networks (Zhou et al., 2024a; Farkas et al., 2018; Sanchez-Garrido et al., 2021).

Potential Applications of TSN in Aerospace is about Intra-Spacecraft Communication and Inter-Spacecraft Communication.

In the Intra-Spacecraft Communication TSN wil be used in:

High performance data transmission: Future aerospace system designs require communication infrastructure that can overcome the limitations of traditional protocols in terms of bandwidth, deployment costs, and flexibility (Sanchez-Garrido et al., 2021). The implementation of TSN Ethernet bus can meet the requirements of micro launch vehicles (Sanchez-Garrido et al., 2021).

Real time control: TSN can provide advanced functions for vehicles, ensuring the certainty and reliable transmission of sensor data and control signals (Li B. et al., 2024).

Integrated Modular Avionics System (IMA): TSN has the potential to serve as an onboard network that interconnects modules in the Integrated Modular Avionics System (IMA) (Zhou et al., 2024b).

Task critical applications: By supporting services with different priorities and QoS, TSN can ensure reliable transmission of critical task data.

In the Inter-Spacecraft Communication TSN wil be used in:

Inter satellite link: TSN can be applied to data links between satellites, providing high reliability and predictability of communication. The formation flight of Earth observation satellites requires the support of inter satellite links (Fiori et al., 2024).

Deep Space Networks: Despite the challenges of long-distance, orbital motion, and harsh environments, deep space communication based on Delay/Interrupt Tolerant Networks (DTNs) can integrate TSNs to achieve networks with intermittent end-to-end connections (Fiori et al., 2024).

Sanchez-Garrido et al. described the design and implementation of a time-sensitive networking (TSN) bus for the avionics of the Miura 1 suborbital micro launcher (Sanchez-Garrido et al., 2021). All these elements have been successfully integrated and validated for the avionics of the Miura 1 sounding rocket, which represents an illustrative case that verifies their applicability to similar scenarios. By providing a comprehensive platform for testing and validation, the testbed will contribute to the advancement of TSN technology in aerospace applications, ultimately improving the safety and efficiency of aircraft operations (Castro-Lara et al., 2025). Therefore, we have every reason to believe that TSN networks can be applied to real-time data processing in space (payload/onboard computers).

3.4 Challenges and future development directions faced by TSN

Although TSN has great potential in the aerospace field, it also faces some challenges:

Environmental adaptability: The special nature of the aerospace environment, such as vacuum, radiation, and extreme temperatures, places higher demands on the reliability of TSN equipment. Future research needs to focus on how to enhance the anti noise capability and adaptability to harsh environments of TSN devices.

Protocol optimization: Standard TSN protocols may require customized optimization to meet specific requirements for aerospace applications. For example, to address the issue of long latency in inter satellite communication, it may be necessary to develop new congestion control and routing algorithms.

Wireless TSN: Expanding TSN to the wireless field and achieving the integration of wired and wireless TSN is an important direction for future development. Wireless TSN can provide flexible real-time communication in scenarios where wiring is inconvenient.

Security issue: Most traffic shaping mechanisms in TSN rely on clock synchronization between different devices in the network. However, time delay attacks (TDA) can interfere with synchronization, thereby reducing the quality of traffic transmission.

4 Current development status of RDMA interconnect bus

4.1 History of RDMA

The concept of RDMA originated in the late 1990s and was initially associated with InfiniBand, a high-speed network technology designed for high-performance computing environments (Santhosh, 2024).

RDMA on Ethernet (RoCE): With the increasing demand for higher performance networks in data centers, there have been attempts to implement RDMA on Ethernet, known as RoCE. RoCE aims to introduce the advantages of RDMA into more widely used Ethernet infrastructure. RoCE has two main versions:

RoCE V1 operates at the Ethernet link layer and relies on Ethernet Priority Flow Control (PFC) to ensure reliable transmission (Hoefler et al., 2023).

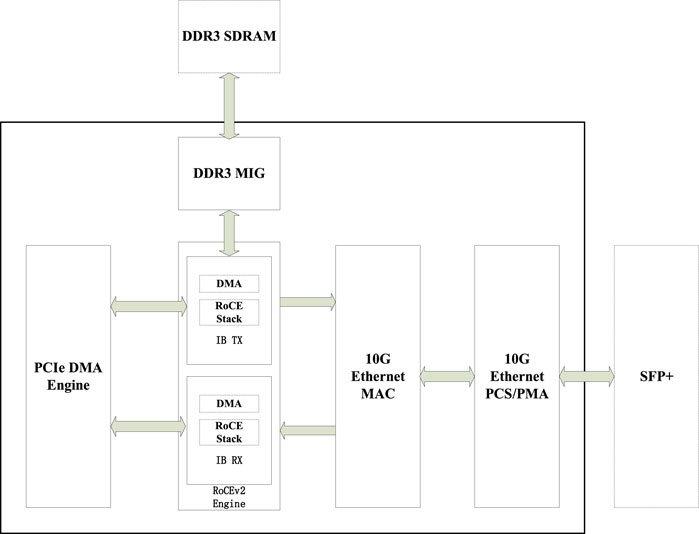

RoCE V2: runs at the IP layer and uses UDP protocol, allowing for deployment in a wider range of network environments, but also requires congestion control mechanisms to ensure performance and reliability (Hoefler et al., 2023). The high-performance network architecture based on RoCEv2 is shown in Figure 4.

4.2 Applications of RDMA

Recent advancements in RDMA include Compute Express Link (CXL) and Non-Volatile Memory Express (NVMe) technologies. Compute Express Link (CXL) is an emerging interconnect technology designed to enhance memory access efficiency in data centers and high-performance computing environments, enabling CPUs and devices (e.g., GPUs and FPGAs) to share memory resources, thereby reducing data replication and improving overall system performance (Hoefler et al., 2023). CXL supports memory pooling/disaggregation, where memory resources can be scaled and allocated independently of compute resources; Non-Volatile Memory Express (NVMe) is a high-speed interface for accessing solid-state drives (SSDs), and NVMe over Fabrics (NVMe-oF) extends NVMe’s performance advantages to distributed storage systems by enabling remote access to NVMe devices via network fabrics (e.g., Ethernet or InfiniBand) (Li Z. et al., 2024). Currently, RDMA technology in China is primarily applied in high-performance computing, data centers, distributed storage systems, and machine learning, where its high bandwidth, low latency, and low CPU overhead play a critical role.

The application scenarios of Remote Direct Memory Access (RDMA) technology in global data centers are diverse, primarily leveraging its ultra-low latency, high bandwidth, and low CPU overhead to optimize data-intensive applications.

Distributed AI Training: Companies such as Meta deploy large-scale RDMA over Converged Ethernet (RoCE) networks for distributed AI training. The rapid growth of AI model scale drives demand for efficient and reliable dedicated network infrastructure. By deeply understanding workloads and translating these insights into the design of network components, efficient AI training can be achieved.

Low-Latency Data Center Communication: RDMA is increasingly adopted in data centers to enable low-latency communication, signifying a major transformation in distributed system construction. However, when pursuing system redesigns driven by new technologies, considerations for system security have not received equal attention. Consequently, it is critical to address the security challenges introduced by RDMA adoption, including changes in Remote Procedure Call (RPC) reliability guarantees and unauthorized data access vulnerabilities (Simpson et al., 2020).

5 Assumption on future high performance interconnected space bus

Current spacecraft electronic systems are undergoing profound transformation, evolving toward distributed, modular, high-reliability, and strong real-time architectures. On one hand, the widespread adoption of advanced high-performance computing units, high-capacity storage arrays, and heterogeneous intelligent payloads based on commercial/industrial-grade components urgently demands an ultra-high-throughput, ultra-low-deterministic-latency interconnection backbone with flexible topology support and robust quality-of-service (QoS) guarantees. On the other hand, missions such as deep-space exploration and constellation networking impose stringent requirements on long-term orbital reliability, autonomous management, and fault tolerance. As a critical subsystem, the bus infrastructure’s robustness, fault-tolerant mechanisms, and maintainability are paramount. Existing technologies like SpaceFibre, while achieving bandwidth improvements (up to 6.25 Gbps), still exhibit significant theoretical and technological gaps in meeting future aerospace demands: terabit-per-second (Tbps) aggregate bandwidth, nanosecond-scale deterministic latency, dynamically reconfigurable topologies, and intelligent self-healing capabilities against multi-level faults in space environments. Furthermore, core high-speed SerDes IPs and radiation-hardened protocol controllers face challenges in domestic R&D autonomy, constraining the comprehensive development of China’s and world’s high-performance onboard bus ecosystem.

Subsequent research on high-performance space interconnection buses should focus on innovative architectures and core technologies for next-generation onboard systems, aiming to overcome traditional bottlenecks and construct foundational information transmission infrastructure supporting future space missions. The research core will revolve around three dimensions: (1) Unified Ultra-High Throughput and Deterministic Latency, exploring ultra-high-speed transmission paths based on photonic/electronic fusion and space-division multiplexing mechanisms; (2) Intelligent Survivability and Autonomous Reconfiguration, designing protocol stacks with nanosecond-scale deterministic guarantees and intelligent traffic shaping capabilities; (3) Multi-Dimensional Integrated Reliability Assurance, constructing intelligent switching cores supporting dynamic topology reconfiguration and multi-path redundancy, while innovating hardware-accelerated end-to-end space-reliable transmission mechanisms such as adaptive forward error correction (FEC), single-event upset (SEU) hardening, and link-level fast switching. Through systematic innovation, this research expects to achieve generational leaps in transmission bandwidth (>10 Tbps aggregate), real-time performance (≤100 ns latency), reliability (99.9999% fault tolerance), and flexibility (microsecond-scale reconfiguration), thereby filling critical global technological gaps in ultra-high-speed, high-reliability, and intelligent onboard interconnection domains.

Based on current research advancements in Time-Sensitive Networking (TSN), Remote Direct Memory Access (RDMA), and space-grade bus technologies, along with future development trends of high-speed computing in spaceborne systems, this paper proposes three feasible research directions:

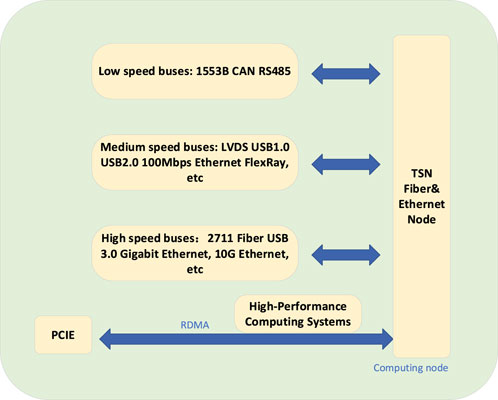

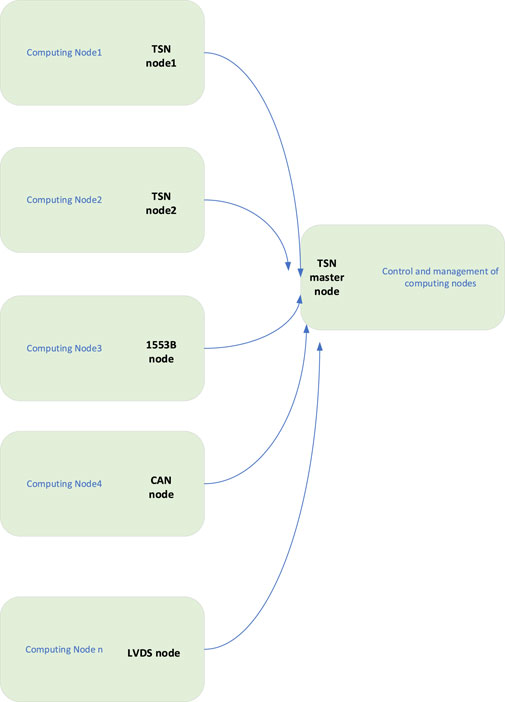

1. Hybrid TSN+RDMA+PCIe architectures are emerging as mainstream solutions, where TSN guarantees deterministic latency (≤1 μs jitter), RDMA enhances throughput (up to 400 Gbps), and PCIe achieves high-speed interconnects for spaceborne devices such as on-board GPU clusters, as shown in Figure 5 (computing system) and Figure 6 (computing nodes);

2. Redundancy protocol optimization through enhanced IEEE 802.1CB (Frame Replication and Elimination for Reliability) mechanisms adapted to space radiation environments, targeting sub-10−9 packet loss rates by implementing hardened SEU-resistant memory buffers and dual-path redundancy switching;

3. Unified protocol integration via TSN gateways to bridge intra-satellite buses (e.g., SpaceWire with 200 Mbps bandwidth) and terrestrial networks (e.g., 5G URLLC with 1 ms latency), reducing inter-satellite data relay latency to ≤5 ms through cross-domain time synchronization and priority-based traffic scheduling

6 Conclusion

This paper is a survey, and a proposal of TSN+RDMA synergy. Based on the current research status of Time-Sensitive Networking (TSN), Remote Direct Memory Access (RDMA), and space-grade bus technologies, along with future development trends toward high-speed and high-performance computing in spaceborne systems, this paper proposes feasible research directions to address complex space environments and advanced mission requirements. These proposals aim to establish a foundation for enhancing high-performance interconnection buses in space applications, while further discussions from the academic community are welcomed to advance this field.

Author contributions

WeZ: Conceptualization, Writing – original draft, Writing – review and editing. WaZ: Investigation, Methodology, Writing – original draft. JR: Methodology, Validation, Writing – original draft. SH: Methodology, Validation, Writing – original draft. WJ: Investigation, Validation, Writing – review and editing. JS: Data curation, Project administration, Writing – original draft. MM: Methodology, Writing – original draft. ZD: Investigation, Validation, Writing – original draft. GY: Software, Writing – original draft. YZ: Supervision, Visualization, Writing – review and editing. JA: Conceptualization, Data curation, Formal Analysis, Project administration, Writing – review and editing.

Funding

The author(s) declare that no financial support was received for the research and/or publication of this article.

Conflict of interest

The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Generative AI statement

The author(s) declare that no Generative AI was used in the creation of this manuscript.

Any alternative text (alt text) provided alongside figures in this article has been generated by Frontiers with the support of artificial intelligence and reasonable efforts have been made to ensure accuracy, including review by the authors wherever possible. If you identify any issues, please contact us.

Publisher’s note

All claims expressed in this article are solely those of the authors and do not necessarily represent those of their affiliated organizations, or those of the publisher, the editors and the reviewers. Any product that may be evaluated in this article, or claim that may be made by its manufacturer, is not guaranteed or endorsed by the publisher.

References

Behbahani, A., Pakmehr, M., and Stange, W. A. (2020). “Optical communications and sensing for avionics”, in Springer handbooks (Springer International Publishing), 1125–1150. doi:10.1007/978-3-030-16250-4_36

Bruckner, D., Stanica, M.-P., Blair, R., Schriegel, S., Kehrer, S., Seewald, M., et al. (2019). An introduction to OPC UA TSN for industrial communication systems. Proc. IEEE 107 (6), 1121–1131. doi:10.1109/jproc.2018.2888703

Castro-Lara, L., Vera-Soto, P., Fortes, S., Escaño, V., Ortiz, R., and Barco, R. (2025). Deployment of a testbed for validation of TSN networks in avionics. Aerospace 12 (3), 186. doi:10.3390/aerospace12030186

Chahed, H., and Kassler, A. (2023). TSN network scheduling—challenges and approaches. Network 3 (4), 585–624. doi:10.3390/network3040026

Chen, Y., Sun, H., Jia, Q., and Shi, G. (2008). “The implementation of a dual-redundaney CAN bus system for space robot”, in Application of electronic technique.

Chen, J., Zhou, Z., Xu, J., Qiu, X., Zhao, T., and Zeng, Z. (2024). “Design of real-time industrial communication system based on TSN”, in 2024 international Conference on power, electrical engineering, electronics and control (PEEEC), 897–901. doi:10.1109/peeec63877.2024.00167

Cossu, G., Gilli, L., Ertunc, E., and Ciaramella, E. (2022). Transporting MIL-STD-1553 signals by means of optical wireless interfaces. IEEE Photonics J. 14 (1), 1–8. doi:10.1109/jphot.2021.3138973

Deng, L., Xie, G., Liu, H., Han, Y., Li, R., and Li, K. (2022). A survey of real-time Ethernet modeling and design methodologies: from AVB to TSN. ACM Comput. Surv. 55 (2), 1–36. doi:10.1145/3487330

Dong-wei, W., Yue-qiang, S., Qi-fei, D., Wei-hua, B., Xian-Yi, W., Di, W., et al. (2012). “A MIL—STD—1553B bus control card design based on BU—61580 and USB”, in Science technology and engineering.

Fangmin, X., Lijiao, W., Fan, Y., and Chenglin, Z. (2020). “Time-sensitive networking (TSN) and wireless TSN technology”, in Telecommunications science.

Farkas, J., Bello, L. L., and Gunther, C. (2018). Time-sensitive networking standards. IEEE Commun. Stand. Mag. 2 (2), 20–21. doi:10.1109/mcomstd.2018.8412457

Fejes, F., Antal, P., and Kerekes, M. (2022). The TSN building Blocks in linux (version 1). arXiv. doi:10.48550/ARXIV.2211.14138

Fiori, T., Lavacca, F. G., Valente, F., and Eramo, V. (2024). Proposal and investigation of a lite time sensitive networking solution for the support of real time services in space launcher networks. IEEE Access 12, 10664–10680. doi:10.1109/access.2024.3353466

Han, K., Mun, H., Balakrishnan, M., and Yeun, C. Y. (2023). Enhancing security and robustness of Cyphal on Controller Area Network in unmanned aerial vehicle environments. Comput. & Secur. 135, 103481. doi:10.1016/j.cose.2023.103481

He, D., Li, X., Chan, S., Gao, J., and Guizani, M. (2019). Security analysis of a space-based wireless network. IEEE Netw. 33 (1), 36–43. doi:10.1109/mnet.2018.1800194

Hoefler, T., Roweth, D., Underwood, K., Alverson, B., Griswold, M., Tabatabaee, V., et al. (2023). Datacenter Ethernet and RDMA: issues at hyperscale (version 2). arXiv. doi:10.48550/ARXIV.2302.03337

Jiang, Z., Wang, Y., Xie, M., Qu, H., and Gu, B. (2020). “A satellite-ground integration test scheme for spacecraft attitude and orbit control system based on 1553B bus architecture”, in Lecture notes in electrical engineering (Singapore: Springer), 3–11. doi:10.1007/978-981-33-4102-9_1

Jiang, J., Li, Y., Zhang, X., Yu, M., Lee, C. D., and Hong, S. H. (2023). Assessing the traffic scheduling method for time-sensitive networking (TSN) by practical implementation. J. Industrial Inf. Integration 33, 100464. doi:10.1016/j.jii.2023.100464

Jin, B., Chen, J., Zhou, Z., Yu, Z., Zhan, P., and Hou, D. (2024). “Design of industrial automation network based on TSN and 5G slice”, in 2024 international conference on power, electrical engineering, electronics and control (PEEEC), 909–914. doi:10.1109/peeec63877.2024.00169

Lan, T., Dong, Z., Zhang, H., and Guo, J. (2021). “An autonomous inter-device bus control transfer protocol for time synchronization 1553B bus network”, in Lecture notes in electrical engineering (Singapore: Springer), 354–361. doi:10.1007/978-981-15-8411-4_45

Levchenko, I., Bazaka, K., Ding, Y., Raitses, Y., Mazouffre, S., Henning, T., et al. (2018). Space micropropulsion systems for Cubesats and small satellites: from proximate targets to furthermost frontiers. Appl. Phys. Rev. 5 (1), 011104. doi:10.1063/1.5007734

Li B, B., Zhu, Y., Liu, Q., and Yao, X. (2024). Development of deterministic communication for in-vehicle networks based on software-defined time-sensitive networking. Machines 12 (11), 816. doi:10.3390/machines12110816

Li, Z., Huang, J., Wang, S., and Wang, J. (2024). Achieving low latency for multipath transmission in RDMA based data center network. IEEE Trans. Cloud Comput. 12 (1), 337–346. doi:10.1109/tcc.2024.3365075

Mifdaoui, A., Frances, F., and Fraboul, C. (2007). “Full duplex switched Ethernet for next generation “1553B”-Based applications”, in 13th IEEE real time and embedded technology and applications symposium (RTAS’07), 45–56. doi:10.1109/rtas.2007.13

Nannipieri, P., Fanucci, L., and Siegle, F. (2020). A representative SpaceFibre network evaluation: features, performances and future trends. Acta Astronaut. 176, 313–323. doi:10.1016/j.actaastro.2020.06.041

Sanchez-Garrido, J., Aparicio, B., Ramirez, J. G., Rodriguez, R., Melara, M., Cercos, L., et al. (2021). Implementation of a time-sensitive networking (TSN) Ethernet bus for microlaunchers. IEEE Trans. Aerosp. Electron. Syst. 57 (5), 2743–2758. doi:10.1109/taes.2021.3061806

Santhosh, K. (2024). Enhancing fault tolerance in RDMA systems through hybrid protocol models. World J. Biol. Pharm. Health Sci. 20 (2), 220–231. doi:10.30574/gjeta.2024.20.2.0140

Sen, S. K. (2021). “CAN bus”, in Fieldbus and networking in process automation (CRC Press), 157–162. doi:10.1201/9781003149941-10

Seoane, L., Diaz, C., Zafra, J., Ibarmia, S., Quintana, C., Canora, C. P., et al. (2021). CAN implementation and performance for Raman laser spectrometer (RLS) instrument on exomars 2020 mission. IEEE Trans. Emerg. Top. Comput. 9 (1), 67–77. doi:10.1109/tetc.2018.2874643

Simpson, A. K., Szekeres, A., Nelson, J., and Zhang, I. (2020). “Securing RDMA for high-performance datacenter storage systems”, in USENIX workshop on hot topics in cloud computing.

Stan, O., Cohen, A., Elovici, Y., and Shabtai, A. (2020). Intrusion detection system for the MIL-STD-1553 communication bus. IEEE Trans. Aerosp. Electron. Syst. 56 (4), 3010–3027. doi:10.1109/taes.2019.2961824

Taylor, G. A., and Thacker, J. C. (1982). Fibre optics systems for space applications. Opt. & Laser Technol. 14 (2), 93–97. doi:10.1016/0030-3992(82)90008-1

Vinaya, S. (2025). Time sensitive networking: revolutionizing industrial automation and automotive systems. World J. Adv. Res. Rev. 26 (2), 303–311. doi:10.30574/wjarr.2025.26.2.1594

Wang, Z., Li, Z., Qiao, X., Zheng, Y., Ai, B., and Song, X. (2024). Time synchronization for 5G and TSN integrated networking (version 1). arXiv. doi:10.48550/ARXIV.2401.17721

Xia, D., Jiang, C., Wan, J., Jin, J., Leung, V. C. M., and Martínez-García, M. (2022). Heterogeneous network access and fusion in smart factory: a survey. ACM Comput. Surv. 55 (6), 1–31. doi:10.1145/3530815

Yang, Y., Duan, Z., and Tehranipoor, M. (2020). Identify a spoofing attack on an in-vehicle CAN bus based on the deep features of an ECU fingerprint signal. Smart Cities 3 (1), 17–30. doi:10.3390/smartcities3010002

Zanbouri, K., Noor-A-Rahim, Md., John, J., Sreenan, C. J., Poor, H. V., and Pesch, D. (2024). A comprehensive survey of wireless time-sensitive networking (TSN): architecture, technologies, applications, and open issues. IEEE Commun. Surv. & Tutorials 27, 2129–2155. doi:10.1109/comst.2024.3486618

Zhang, T., Wang, G., Xue, C., Wang, J., Nixon, M., and Han, S. (2024). Time-sensitive networking (TSN) for industrial automation: current advances and future directions. ACM Comput. Surv. 57 (2), 1–38. doi:10.1145/3695248

Zheng, L., Chen, X., and Lv, X. H. (2011). Research on internal communication of redundant flight control computer for UAV. Adv. Mater. Res. 383–390, 1578–1583. doi:10.4028/www.scientific.net/amr.383-390.1578

Zheng, J., An, J., and Jiang, Y. (2022). An efficient multi-lane SpaceFibre core for spacecraft data-handling networks. Electronics 11 (9), 1410. doi:10.3390/electronics11091410

Zhou, X., He, F., Zhao, L., and Li, E. (2024a). Hybrid scheduling of tasks and messages for TSN-based avionics systems. IEEE Trans. Industrial Inf. 20 (2), 1081–1092. doi:10.1109/tii.2023.3254608

Keywords: TSN (time-sensitive networking), RDMA (remote direct memory access), high-performance computing, high-efficiency data processing, high-performance interconnection bus

Citation: Zhao W, Zhang W, Rao J, Han S, Jia W, Song J, Ma M, Dong Z, Yin G, Zhu Y and An J (2025) Current development status of key technologies for high-performance on-board interconnection buses — analysis of TSN bus application prospects in aerospace. Front. Astron. Space Sci. 12:1676898. doi: 10.3389/fspas.2025.1676898

Received: 31 July 2025; Accepted: 22 September 2025;

Published: 02 October 2025.

Edited by:

Gordon James Thorogood, Australian Nuclear Science and Technology Organisation, AustraliaReviewed by:

Mohamed Seliem, University College Cork, IrelandCopyright © 2025 Zhao, Zhang, Rao, Han, Jia, Song, Ma, Dong, Yin, Zhu and An. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.

*Correspondence: Jianing Rao, cmFvamlhbmluZ0Buc3NjLmFjLmNu

Wenjie Zhao

Wenjie Zhao Wanying Zhang1

Wanying Zhang1 Jianing Rao

Jianing Rao